「SoC」or「SoC」?統合へのさまざまな道:SYSTEM DESIGN JOURNAL(3/4 ページ)

InFOに見るデザインフローの重要性

通常のサブストレート上にピッチの広いインタコネクトがあれば十分という場合は、潜在的により低コストのマルチダイアプローチがあります。1つはTSMCのInFO(Integrated Fan-Out)パッケージングです。

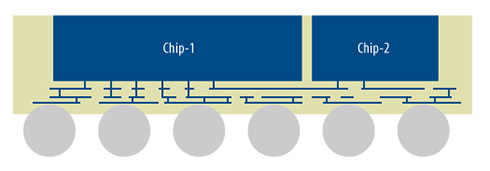

InFOは、もともと通常のファンアウトパッケージをウェハスケールで製造するために設計されたものですが、マルチダイウェハレベルパッケージングの提供が計画されています。このプロセスでは、各種ダイを合成ウェハ上の目的の位置で上向きに固定します。

次に、必要に応じて複数の層を使用してダイ間のインタコネクトを組み込みながら、ウェハの上に多層サブストレートを重ねます。ビルドアップの最上層にパッケージはんだボールを配置した後、個々のマルチダイアセンブリを分離し、合成ウェハ基材から切り離し、全てをパッシベーションすれば、ウェハスケールの効率で2.5Dモジュールが得られます(図2)。

これら技術の重要な考慮事項の1つはデザインフローです。

ダイ間接続がシステムの一部になるため、ダイを切り離して設計することはできません。正確な遅延モデリングと消費電力モデリング、場合によっては熱モデリング、機械モデリング、電磁モデリングが不可欠であり、しかもチップデザインと協調して行う必要があります。TSMCは最近のEcosystem Forumにおいて、比較的単純なInFOパッケージであっても、チップとパッケージの協調設計を強く推奨しています。

シリアルの選択肢

CoWoSとInFOを比較すると、必要なダイ間接続が少ないほど、パッケージングや解析に費やさなければならない労力は少なく済むことは明らかです。従って、少ないワイヤで超高速データレートを実現できる高速シリアルトランシーバーは、レイテンシが増加するものの非常に重要な手段となります。シリアルトランシーバーを使用すれば、1ペアの導体で28Gbpsのデータレートを実現することが可能であり、今後もさらなる高速化が見込まれています。

ボード設計会社であるSpeedingEdgeの創設者 LeeRitchey氏はSEMICO IMPACTのパネルディスカッションにおいて「2016年までに、56Gbpsを使用した量産システムが登場すると思いますが、それまでに、28Gbpsは一般的なものになっているでしょう」と述べています。

ディスカッションに同席していたTeraspeedのコンサルタント Scott McMorrow氏は、56Gbpsでも実用限界に達しない可能性を示し、「モデリングによれば、10インチ程度の距離までは56Gbpsを維持できますが、理論上は従来のICパッケージから110Gbpsで接続することも可能です」と発言しています。

シリアルリンクでは、距離や電気的複雑さが大きな違いを生みます。Mentor Graphicsの主席エンジニア DanieldeAraujo氏は、同パネルにおいて「新たなスピードは最も簡単な部分に最初に現れます。56Gbpsはまずチップ-モジュール間接続、次いでボード上に採用されるでしょう。コネクタやバックプレーンを横断するのは、さらに先のことになりそうです」と述べています。

実際、2.5Dモジュールの内部には、かなり前から中速のシリアルリンクが使用されています。しかし、2.5Dモジュール内のインタコネクトが非常にクリーンで短い可能性を考えると、スピードの制約要因はチャネルよりむしろトランシーバーや消費電力の考慮なのかもしれません。

マルチダイモジュールの聖域を抜けた後は、高いデータレートはますます実現困難になります。Ritchey氏が「問題は損失ではなく、むしろスキューやクロストークです」と述べると、McMorrow氏はすかさず同意し、「回路ボード材料のばらつきや異方性が原因で、スキューを4ps未満に抑えることは非常に困難です。かといって、スキューをほんの少し大きくするだけで動作しなくなります」と説明しました。

一部の研究者はポリテトラフルオロエチレン(PTFE)など、均一性と等方性が非常に高い新たなボード材料に取り組むことで、この限界に挑戦しています。しかし、業界全般として、そうした材料を扱うための設備も経験もありません。

関連記事

組み込みコンピューティングに向けた、ハードウェアアクセラレーションの選択肢

組み込みコンピューティングに向けた、ハードウェアアクセラレーションの選択肢

組み込みコンピューティングを加速させるハードウェア・アーキテクチャとは何でしょうか。DSP?GPU?それともメニーコアでしょうか。どのアプローチが最も適するのかを考察します。 FinFET革命がコンピュータアーキテクチャを変える

FinFET革命がコンピュータアーキテクチャを変える

FinFETの登場により、ムーアの法則はまだ継続される見通しです。ですが、それで全てが解決するわけではありません。FinFETの登場が、大きなSoCを自律的な機能ブロックに分割するという方向に導く結果となるでしょう。 サブシステムIPがチップの境界を越える

サブシステムIPがチップの境界を越える

サブシステム規模のIP(サブシステムIP)はSoCはもちろん、FPGAにまでも影響を与えています。素晴らしい取り組みですが、さまざまな注意点も存在します。スムーズな実装を行うための4つの注意点について述べます。 畳み込みニューラルネットワークの使い方、分かりますか?

畳み込みニューラルネットワークの使い方、分かりますか?

畳み込みニューラルネットワークとは何でしょうか。学問の世界から現実の世界に登場しつつあるこれは、さまざまな組み込みシステムに利用される可能性が高く、大いに関心を持つべきです。 組み込みにおけるコンピュータビジョンを整理する

組み込みにおけるコンピュータビジョンを整理する

画像認識(コンピュータビジョン、マシンビジョン)の需要は高まっており、その方法はさまざまです。画像による入力を有用なものとする実装方法について分類と整理を試みます。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 40台超のロボットを統合管理する自律運用システムが本格稼働

- 4年目を迎えた「小さく始めるAIパビリオン」、マイコンよりMPU多めの構成に

コーナーリンク