解析実行エラーの原因と対策(その4):SPICEの仕組みとその活用設計(9)(2/3 ページ)

ウィーンブリッジ回路の例

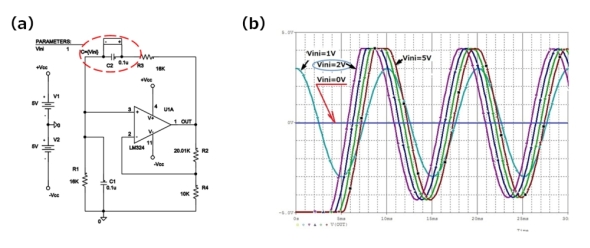

図4に示す“ウィーンブリッジ”もまた、代表的な正帰還回路です。遅れ要素のC1、R1と、進み要素のC2、R3を利用してノイズを選択/帰還させて正弦波を得る回路として以前はよく用いられていました。

SPICE上ではノイズがありませんから、容量C2に初期電圧{Vini}を与えて発振状態へ移行させます。Viniを変化させてみると、0Vでは発振は開始せず、1Vでは振幅不足です。結局、2V以上の初期電圧が必要であることが分かります。実回路のウィーンブリッジも波形をひずみなく安定に保つのは難しく、熱的フィードバックを掛けたり、非線形フィードバックを掛けたりします。回路のR2が20Kより微妙に大きくなっているのは、発振を成長させるためです。ただ発振するだけでは不十分であり、結果が正しいのか否かを判断できるだけの解析が必要なのです(2V以上では回路のクリップが見られ、十分な振幅が得られることが分かります)。

図4 ウィーンブリッジの回路例と応答波形。(a)の回路図ではC2のバイアス{Vini}を0〜5Vまで1V刻みで設定。(b)の解析波形では、Viniが0Vでは発振せず、1Vでは振幅不足となる。2V以上であれば、振幅−4.2〜4Vまでの十分な振幅が得られる(クリックで拡大)

図4 ウィーンブリッジの回路例と応答波形。(a)の回路図ではC2のバイアス{Vini}を0〜5Vまで1V刻みで設定。(b)の解析波形では、Viniが0Vでは発振せず、1Vでは振幅不足となる。2V以上であれば、振幅−4.2〜4Vまでの十分な振幅が得られる(クリックで拡大)図1〜4の例からも分かるように、正帰還を利用した回路を解析する場合は先に理論的にどのような波形になるのかを算出し、一度は解析波形と比較しておくことが必要なのが分かります。回路が複雑で理論波形が算出できない場合は、部分々々の波形を比較し、“V&V(Verification and Validation:検証と妥当性確認)”の一助としてください。

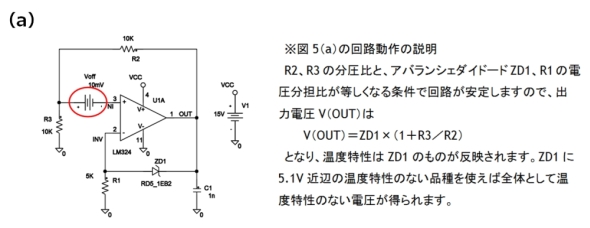

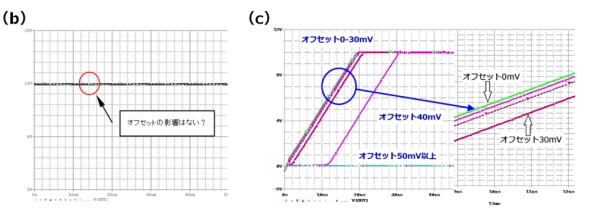

次の図5の例は、電源の立ち上げ方によっては実際の回路の様子を再現できない、安定化電源回路の過渡解析の事例です。

図5(a)の安定化電源回路は、制御部にオペアンプを使っていますので、入力端子間のオフセット電圧が出力電圧にどの程度影響を与えるかを過渡解析で検討します。オフセット電圧が出力電圧を負に振る方向なら正帰還を用いている関係で出力電圧が上昇しないからです(なお、このオフセット限界値はZD1のモデルを替えると変化します)。

回路の動作電源VCCをDC電源で立ち上げたものを図5(b)に、より実際に近い10μSのテーパーで立ち上げたものを図5(c)に示します。しかし、2つの解析結果を比較すると、オフセット電圧の許容値が全く異なります。どちらが実際を表現しているかは明らかです。

原因はDC電源を用いたため、解析初期のバイアス計算にVCCが印加されている状態での条件が使われ、出力電圧が立ち上がった状態で計算されてしまう点にあります。

実際のDC電源は有限の立ち上がり時間を持つ電源であるにもかかわらず、回路図上では理想DC電源になっている場合がほとんどです。しかし、このような配慮が必要になるケースは以外に多いのです。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- なぜオムロンは農業の“作業”ではなく“判断”の自動化を目指すのか

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

コーナーリンク