第18回 CADデータの統合:前田真一の最新実装技術あれこれ塾(2/3 ページ)

2. ハードとソフトの協調設計

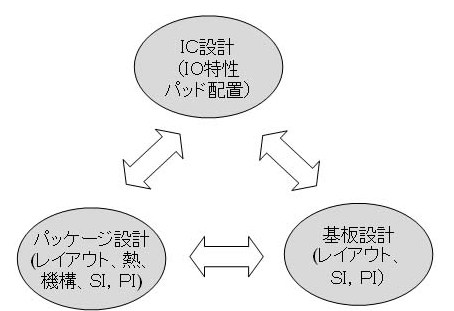

電子回路の設計において基板とICパッケージ(インターポーザー)、ASICの設計を協調して設計する、協調設計手法が提案されています(図8)。

しかし、このような電子回路の設計だけではなく、機器や装置全体の開発で見ると、もっと大きな協調設計が重要になっています。つまり、電気とメカ、ソフトの協調設計です。

多くの機能を1チップに総合するSoCの開発では、SoCに内蔵されているマイクロプロセッサ上で走らせるソフトの開発がチップ内の回路開発と並び大変重要なものとなります。SoCでは、ハードとソフトが協調してデータ処理を行うことが普通の状態です。SoCはハードとソフトを別々に開発する方が不自然です。

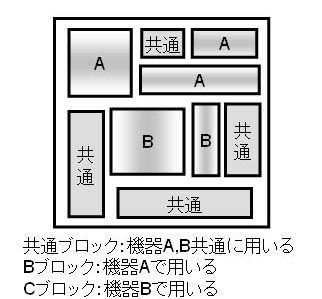

さらに、SoCのハードとソフトの設計を困難にして、協調設計が必要になる要件があります。ICの集積度が飛躍的に向上して、1チップに収められるシステムの規模が大きくなりました。それに従い、SoCの開発コストが膨大なものとってしまいました。今、多くのSoCでは開発コストが膨大になり、設計コストが製品で回収しきれない状態が発生するようになってしまいました。開発コストを製品で回収するためには、チップを大量に製造して、チップ単価当たりの設計コストを下げる必要があります。幸いなことにチップに集積できる回路規模が大きくなったので、機能が異なる複数の機種で同じASICを使い、ソフトでおのおのの機種に適した機能を切り替えるようにします(図9)。

このようにすることで、開発費はある程度上昇するものの、複数のASICを個別に開発するよりは大幅に開発費を下げることができます。これは、ソフトによりハードの部分を動作させたり、止めたりしているわけです。ASIC消費電力を下げるためにも、使わない回路と使う回路の制御はきめ細かくする必要があります。

このように、回路の動作とソフトの動作は密接に連携しているため、不具合が生じた場合、回路のバグとソフトのバグの切り分けが重要になります。不具合の多くはハード設計とソフト開発の間の意思の疎通が原因となります。

3. メカと電気の協調設計

メカと電気の協調設計は昔から行われてきました。基板の外形や、取り付け穴、コネクタの位置などは筐体設計の条件から決まるものです。

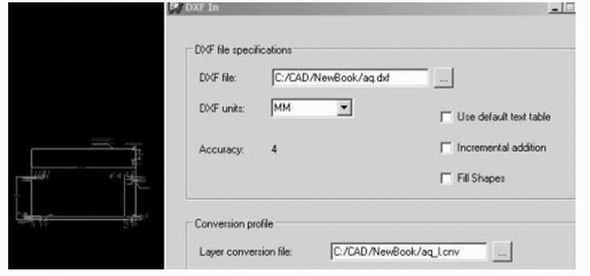

このため、多くの基板設計CADシステムは機構CADデータからの基板外形や基板取り付けねじ穴、配線禁止領域など2次元のデータ読み込み機能をサポートしています(図10)。

しかし、これは協調設計と呼ばれるレベルではなく、単に機構設計データに結果の一部を基板設計CADが読み込めるという一方向のデータ変換だけです。

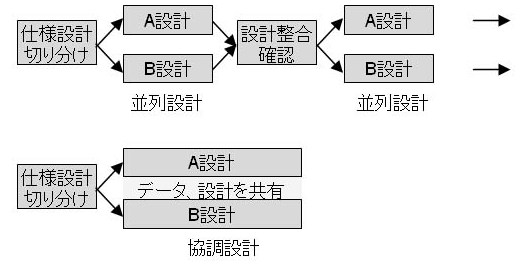

協調設計は、双方向にデータや情報をやり取りしながら並列的に設計を進めたり、さらには同じデータを共用して共同設計をしたりする手法です(図11)。

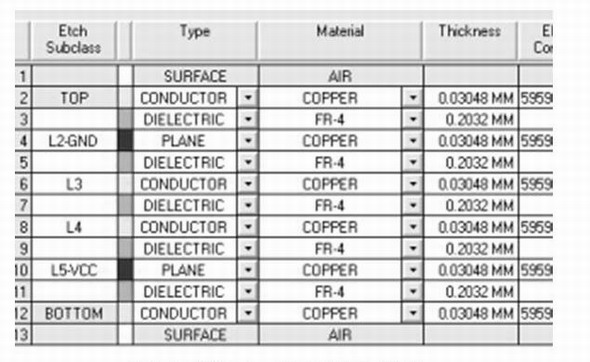

実際、最近では、より密接なメカ系CADと電気系CADのデータの互換が求められてきました。機構系CADでは2次元から3次元への移行が進められ、現在は3次元データを扱っています。それに対し、電気系CADではせいぜいビューアとして使う以外は3次元データの必要はなく、2次元(2.5次元)のデータで十分でした(図12)。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- あの金型今どこ? もう何年使ってない? かつての慣習が法令違反になる理由

- 産業用AIの競争優位性を示す、ハノーバーメッセ 2026が開幕

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- 滋賀本社に新工場、5面加工門形マシニングなど導入し大型部品の一貫生産強化

- 半導体製造投資、続々――経産省やLSTC企業も動き出し、列島が沸く

- 安川電機がEthernet通信標準搭載の小型インバーター、主要プロトコルに対応

- 牧野フライスTOBに中止勧告、投資ファンド「大きな驚きをもって受け止め」

- 用途に応じて“みこし”を付け替え、国産300kg可搬のAMRの予約受付開始

- 後工程で高まる精度要求、半導体“積層化”支える2次元スケールで描く成長曲線

コーナーリンク

図8 電気系の協調設計

図8 電気系の協調設計 図9 複数のASICをまとめて共通設計

図9 複数のASICをまとめて共通設計 図10 基板CADの機構CADデータ入力機構 (Allegro DXF In)

図10 基板CADの機構CADデータ入力機構 (Allegro DXF In) 図11 並列設計と協調設計

図11 並列設計と協調設計 図12 基板データは2.5次元構造 (Allegroの層構成表示)

図12 基板データは2.5次元構造 (Allegroの層構成表示)