第11回 LSI消費電力把握の必要性と試み:前田真一の最新実装技術あれこれ塾(1/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第11回は、第10回に続き、LSIの消費電力についてさらに詳しく解説する。

本連載は「エレクトロニクス実装技術」2012年2月号の記事を転載しています。

1. LSIの消費電力

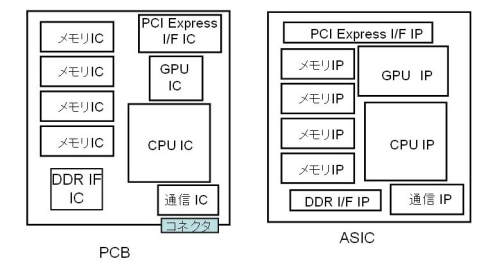

基板では各社のICを搭載し、それらIC間を基板配線で接続してシステムを組み上げます。それと同じようにシステムIC(システムLSIとも)は各社のIP(Intellectual Property)をシリコンチップの上に配置し、それらIP間の配線をシリコン上の配線で接続してシステムを組み上げています(図1)。

IC部品と同じようにIPも入出力特性、電源条件、消費電力などのデータ、論理・タイミング解析用のモデル、レイアウトマスクなどのデータが用意されています。IPという部品を集めてシステムに組み上げたASICの消費電力は、ICという部品を組み合わせてシステムを作成した基板の消費電力と同じように考えることができます。基板の消費電力は基板に搭載されているIC個々の消費電力をすべて合計したものではありません。部品としてのICで示されている定格電流(電力)は、そのICが最大稼働している状態での最大消費電流値です。

基板システムは基板上に搭載されているすべてのICが常に最大負荷で稼働している状態はありえません。例えば動作が簡単なDDRメモリを例に考えてみましょう。

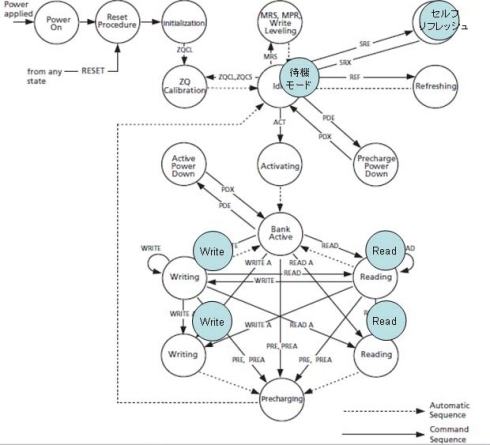

DDRメモリでは大きく分けてデータ書き込み時、データ読み出し時、コマンドを受けて動作モードを切り替え時、待機時、データのリフレッシュ時などの主な動作モードがあります。データ書き込み時やデータ読み出し時に最も多くの電力を消費します。さらにこのモードの中でもアドレス指定時、内部データ入出力時、IO回路動作時など消費電力にむらがあります(図2)。

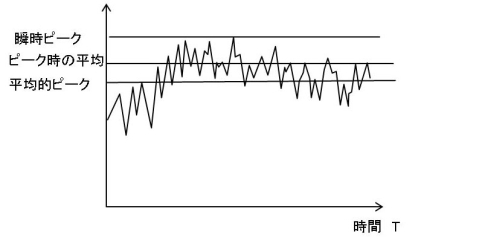

メモリの消費電力を表すとき、この最大に電力を消費するモードの平均値を表すのか、その中での瞬間ピーク値を表すのか、ワーストケースを見込んで、さらにいくらか多めに見るのか、あまり厳密な定義は決まっていません(図3)。

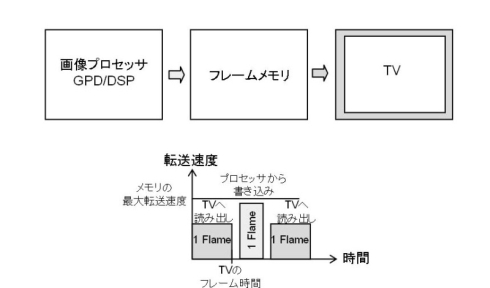

さらに、メモリは通常最大速度で長時間Read/Writeを持続し続けているわけではありません。例えば、最もメモリを頻繁に使うと思われる画像メモリですが、画像の表示速度はメモリの最大転送速度よりは遅くなっています。このため、1フレーム分のデータを読み込んでしまえば、このフレーム表示が終了して新しいフレームデータが必要になるまでは、休止しています(図4)。

また、この機器が、動画表示モードからテキスト表示モードに切り替われば、画面はほとんど変化しないので、メモリの稼働はずっと遅くなります。さらに音声モードや楽曲モードになれば、画面表示はなくなり、フレームメモリは休止状態になります。

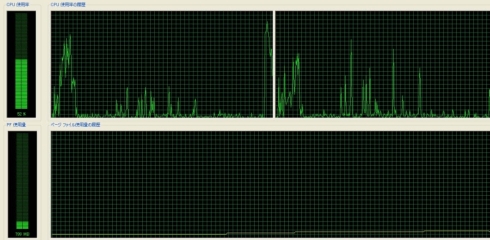

実際のシステムではメモリの平均消費電力は、スペックにあるメモリの最大消費電力よりは大幅に少なくなります。基板上のCPUやインタフェースICなど、他のICでも同じように稼働している時でも最大定格ほどの電力は使わないし、まったく稼働していない時間も多くあります(図5)。

設計時に基板の消費電力を正確に見積もることは困難で、多くの場合には、前に設計した基板の消費電力から変更するICの差分を考慮して概算値を求めるとか、大まかに、各ICの消費電力を合計したものの50%とか70%として見積もっています。実際の基板の消費電力は、多くの場合、試作機ができた時点で実測をした結果を基に稼働率などを考え、概算しているのが実情です。

消費電力の見積もりの困難さは、多くのIPブロックを組み合わせて合成されたASICでも同じことがいえます。ASICの消費電力はおのおののIPの消費電力を単純に加算した合計よりはずっと少ないものになります。

メモリやCPUでもいろいろな動作モードはあり、おのおのの動作モードにより消費電力が異なりますが、これらのメモリやCPUを組み込むASICの動作モードはさらに複雑です。

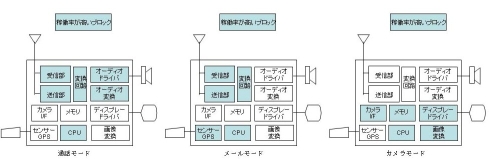

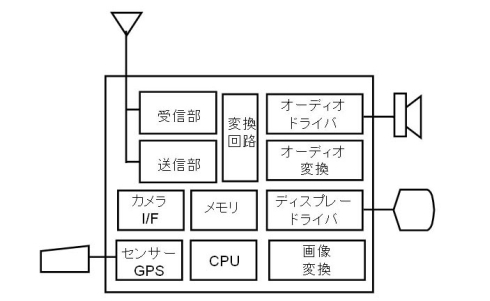

ASICではすべての機能回路ブロックが同時に同じ稼働率で動いているわけではありません。例えばスマートフォンで使うASICが図6のブロック構造になっているとします。このASICは、待ち受け時には受信部だけが動いています。通話を受けると、着信を知らせるブザーやバイブレータのオーディオドライバが稼働します。その後、ディスプレイがONになり、発信者を表示します。

通話状態になると、送信回路と受信回路、信号変換回路のほか、ディスプレイ回路、オーディオ回路がONになります。カメラモードでは、カメラI/Fが動作します。動画の送受信では画像変換回路が動作します。インターネットアクセスでは受信回路とCPU、ゲームやアプリ実行ではCPUの負荷が大きくなります(図7)。

ASICの消費電力低減では各モードに応じて動作していない回路ブロックの消費電力を極限まで削減します。この削減には、クロックを遅くして、動作を遅くする、電源電圧を落として、動作を遅くしたり、待機モードにしたりする、電源を落として停止状態にする、などの方法があります。

これらの制御は、IPごとに行われますが、IPの設計によって、電源をどこまで低下できるのか、1つのIPだけの電源を落とすことができるのか、IP間の接続で、接続されているIPの電源が落ちたり、電圧が低下したりしても良いのかなど、多くの場合があります。

さらに、各IPはおのおの異なる会社が設計していますから、IP間の接続に対してIPが電源電圧を低下させたり、落としたりした場合の動作や、他のIPに対する影響がデータとして開示されている必要があります。

これらの情報の共通化や設計手法が重要となってきています。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

コーナーリンク

図3 ICの消費電力はどれ?

図3 ICの消費電力はどれ?

図6 ASICの例

図6 ASICの例