実装ラインの段取り替え計画立案が数秒で完了、NECがアニーリングマシンで実現:製造ITニュース(2/2 ページ)

「SX-Aurora TSUBASA」は300倍以上高速、10万量子ビットに対応

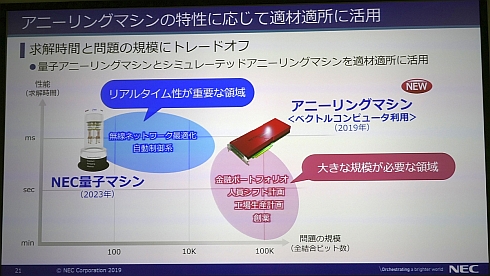

ただし、組み合わせ最適化問題で量子コンピュータが必要になるのはリアルタイム性が要求される用途だ。そこまでリアルタイム性が必要なく、より規模の大きな問題に適用するのであれば、従来のシリコン半導体技術を用いたアニーリングマシンでも対応が可能だ。

NECが提供するSX-Aurora TSUBASAを用いたSAマシンは、インテルのXeonプロセッサを用いる場合と比べて300倍以上高速の処理が可能で、SX-Aurora TSUBASA1台当たり10万量子ビット相当の組み合わせ最適化問題に対応できるという。西原氏は「SX-Aurora TSUBASAはスーパーコンピュータなので、従来通りにシミュレーションや機械学習などのアプリケーションにも利用できる。将来の高速コンピューティングプラットフォームは、最適なコンピューティング技術で適切に課題を解くことが重要であり、そういった連携アプリケーションを開発するのも容易だろう」と説明する。

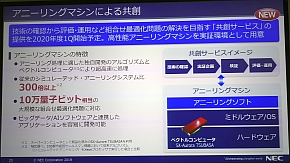

「SX-Aurora TSUBASA」を用いたSAマシンによる共創サービスの概要(左)。PCに組み込んだSX-Aurora TSUBASAを使って、組み合わせ最適化問題を解く様子も見せた(右)(クリックで拡大) 出典:NEC

「SX-Aurora TSUBASA」を用いたSAマシンによる共創サービスの概要(左)。PCに組み込んだSX-Aurora TSUBASAを使って、組み合わせ最適化問題を解く様子も見せた(右)(クリックで拡大) 出典:NEC多品種変量生産で増える表面実装ラインの段取り替えに適用

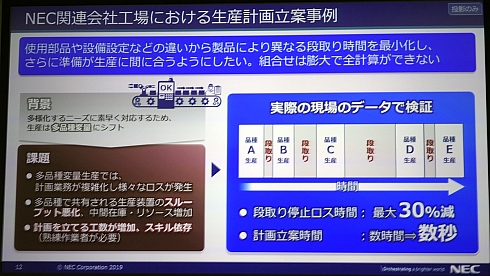

会見では、NECで生産を担うNECプラットフォームズの工場で実施した、表面実装ラインの生産計画立案への適用例が紹介された。

表面実装ラインでは生産品種が変わるごとに、搭載する部品などを変更するための段取り替えを行う必要がある。近年では、NECの工場でも多品種変量生産が求められており、そのためには段取り替えを頻繁に行わなければならない。従来は、この段取り替えの計画は熟練技術者が数時間をかけて立案していた。

段取り替えの計画立案は、まさに量子コンピューティング技術が得意とする組み合わせ最適化問題である。NECは、これまでの段取り替えデータを基に、5000〜1万量子ビットのSAマシンを用いて段取り替えの計画立案を実施した。その結果、計画立案時間は数秒に短縮でき、その計画内容についても段取り替えによる生産ラインの停止時間を最大30%削減できたという。

関連記事

かつて世界一を支えたNECのベクトル演算技術、いま「次世代イノベーション」を担う

かつて世界一を支えたNECのベクトル演算技術、いま「次世代イノベーション」を担う

同社が東京都内で開催したユーザーイベント「C&Cユーザーフォーラム&iEXPO2019」(2019年11月7〜8日)では、最新の「SX-Aurora TSUBASA」アーキテクチャを搭載したベクトルプロセッサなどを展示。また、2019年11月1日からはメモリ帯域を強化した新製品の受注も開始している。 量子コンピュータとAI、先進技術における日本の最新動向と位置付け

量子コンピュータとAI、先進技術における日本の最新動向と位置付け

日本最大級の産学官連携イベント「イノベーション・ジャパン2019」(2019年8月29〜30日、東京ビッグサイト青海展示棟)において、科学技術振興機構(JST)事業セミナーで、JST研究開発戦略センター(CRDS)がAI技術および量子コンピュータ技術の最新動向について紹介した。 量子コンピューティングは製造業でも活用進む、その可能性と現実

量子コンピューティングは製造業でも活用進む、その可能性と現実

次世代のコンピューティング技術として注目を集める「量子コンピュータ」。製造業にとっての量子コンピュータの可能性について、ザイナス イノベーション事業部 部長で量子計算コンサルタントの畔上文昭氏に、製造業での量子コンピューティング技術の活用動向と現実について話を聞いた。 生産計画など複雑な“組み合わせ問題”を解決、量子コンピューティングの力

生産計画など複雑な“組み合わせ問題”を解決、量子コンピューティングの力

富士通は2019年5月14日、同社のユーザーイベントである「富士通フォーラム2019 東京」(2019年5月16〜17日、東京国際フォーラム)の内覧会を実施。その中で量子コンピューティング技術を疑似的に応用した「デジタルアニーラ」への取り組みを紹介した。 量子コンピュータって実際のところ何? NECもアニーリングに注力

量子コンピュータって実際のところ何? NECもアニーリングに注力

NECは2019年1月16日、報道陣を対象として量子コンピュータに関する勉強会を開催し、同社が注力する超伝導パラメトロン素子を活用した量子アニーリングマシンの特徴と優位性を訴求した。同社は同マシンについて2023年の実用化を目指す方針だ。 量子コンピュータでなぜAIは進化するのか、全ての鍵は「最適化問題」

量子コンピュータでなぜAIは進化するのか、全ての鍵は「最適化問題」

「CEATEC JAPAN 2017」の自動運転技術に関するカンファレンスで、東北大学大学院 准教授の大関真之氏が登壇し、「量子アニーリングが拓く機械学習と計算技術の新時代」をテーマに講演を行った。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

製造マネジメントの記事ランキング

- 数カ月掛かっていた計画業務がわずか2時間に NEC「BluStellar」の“進化と深化”

- ソニーとTSMCが新たな合弁検討、半導体のファブライト化とフィジカルAI見据え

- 三菱電機が過去最高更新、データセンター需要とFA回復がけん引し成長戦略を加速

- EV開発を中止しても、ソニーグループがソニー・ホンダを「良い経験」とする理由

- ソニーグループ、売上高と営業利益で過去最高 ゲームとイメージセンサーがけん引

- 「誰がそのコード書いたんだい?」AI時代だから求められるOSS管理

- 「OSSを安心して使えない」から脱却へ、カギを握る「OSPO」とは何か

- LIXILが榎戸工場で衛生陶器廃材を100%再資源化し「陶器から陶器へ」を実現

- Industry 4.0を体現 SAPの最新ソリューションが体験できる施設がリニューアル

- 脱アナログ管理で生産性25%向上、パナソニック流「自走する工場」の作り方

コーナーリンク