ルネサスが新たなエッジAI技術を開発、世界最高クラスの電力効率と推論精度:人工知能ニュース(3/4 ページ)

誤差が少ないSRAM演算回路ブロックに発火ニューロンを配置

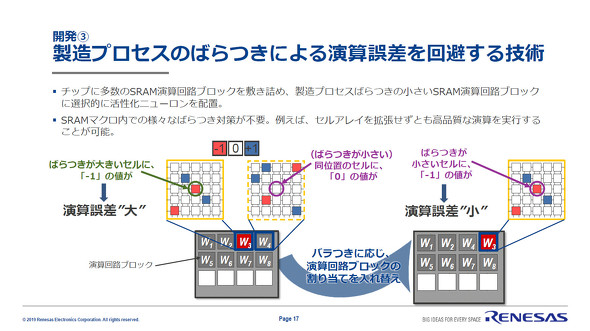

また、製造プロセスのばらつきが積和演算の結果に誤差を生じさせることがある。これは、製造プロセスのばらつきによってビット線電流の値に誤差が生じ、メモリデータの読み出しにも誤りが発生するためだ。

そこで、同技術ではチップ内に多数のSRAM演算回路ブロックを敷き詰め、製造プロセスのばらつきが小さい演算回路ブロックで演算を行う手法を開発した。発火するニューロンにはばらつきの小さい演算回路ブロックを選択的に配置し、ニューラルネットワークのほとんどを占める発火しないニューロンにばらつきが大きい演算回路ブロックを配置する。これにより冗長処理などSRAMマクロ上での対策を不要としつつ、無視可能なレベルまで演算誤差が低減できるという。

高い推論精度と優れた電力効率を両立

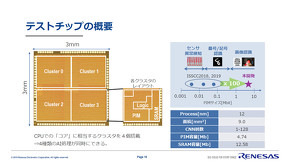

ルネサスは同技術を用いたテストチップを既に開発している。製造プロセスは12nmでチップサイズは3×3mm。同チップはCPUにおける「コア」に相当するクラスターを4個搭載しており、1つのクラスターで隠れ層が1層から32層までのCNN処理に対応できる。演算ユニット単体での電力効率は79.3TOPS/Wで、1.5ビット演算精度におけるCNN処理時の実行電力効率は8.8TOPS/Wと優れた値を示している。

既報の研究ではPIM容量のオーダーが0.001M〜0.1Mビットクラスで、センサーの異常検知やMNIST(画像認識アルゴリズムのベンチマークに使われる手書き数字画像データセット)の数字認識など、入力データが比較的小規模なニューラルネットワークの実行を行っていた。ルネサスが今回開発したテストチップはPIM容量が4.74Mビット(SRAM容量は12.58Mビット)で、既報研究から100倍程度の演算規模を持つ。同社担当者は「従来研究のテストチップは原理実証を目的としており、ニューラルネットワークの処理を完結する機能はなかった。われわれのテストチップはメモリなどCNNの実行に必要な機能をそろえ、システムレベルで動作できる」と成果を語る。

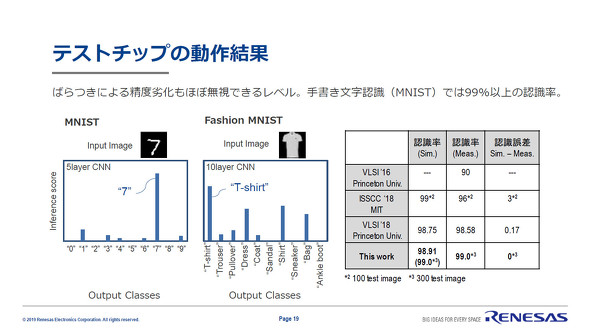

このテストチップを演算精度4ビットで動作させ、MNIST(画像認識アルゴリズムのベンチマークに使われる手書き数字画像データセット)とFashion MNIST(画像認識アルゴリズムのベンチマークに使われる手書き数字画像データセット)によって推論精度を評価したところ、認識率は99%以上となった。また、「既報の研究でシミュレーション上の認識精度からテストチップの認識精度が低下するケースがあるが、本研究ではほぼ同一だ。これにより、製造プロセスのばらつきによる精度影響が回避できていることが分かる」(同社担当者)とする。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- イチから全部作ってみよう(31)SQLを操作して実際にデータベースを作ってみる

- “Rapidusパーク”の先駆けとなるか、LSTCが千歳市内に光電融合技術の拠点開設

- 産総研のフィジカルAIプロジェクトに迫る 10万年ギャップを超えろ!

- オープンソースの「Godot」をベースに強化した産業用リアルタイム3Dエンジン

- Arm初のCPUチップ「AGI CPU」が顧客とパートナーにもたらす悲喜こもごも

- フィジカルAI開発支援に向け「Omniverse」や「Isaac Sim」のPoC環境を無償提供

- アミューズメント機器のコイン投入量や景品出庫数をリアルタイム可視化

- 24時間連続稼働を想定したファンレスの組み込み用コントローラーを発売

- 「プリクラ」、実は高度な技術の塊だった件

- 「GoogleTest」の活用を支援するC/C++言語対応テストツール

コーナーリンク