よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる:MAX 10 FPGAで学ぶFPGA開発入門(5)(6/6 ページ)

オシロでタイミング測定

さて、これでプログラム的には動いたのだが、タイミング的にはどうだろう(普通はまず設計段階でタイミングを見るわけだが、あえて逆にまず実際の動作の状況を見ることにする)。

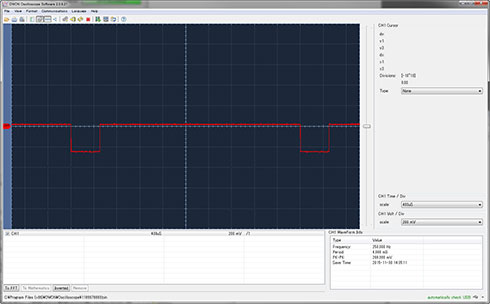

下のPhoto03はLEDの4・9番ピン(小数点)の信号をオシロスコープで見てみたところ。トリガーは信号の立下りである(アノードコモンなので、Levelが0になるとLEDが電流に流れるため)。右下にあるように、Periodは4.000msとなっている。8つのセグメントを4.000msごとに更新するということは、1つのセグメントあたり0.500msごとに更新しているということで、これはプログラム通りの結果になっていることが分かる。

Photo03:ちなみにオシロスコープ本体の方で細かく情報を表示させると、信号がOffになっている期間は平均0.496msということで、きっちり0.5msにはならない模様。とはいえ、ぎりぎりまで発光していることが分かる

Photo03:ちなみにオシロスコープ本体の方で細かく情報を表示させると、信号がOffになっている期間は平均0.496msということで、きっちり0.5msにはならない模様。とはいえ、ぎりぎりまで発光していることが分かるこの工作程度だと「これでOK、万々歳」ということになるのだが、複雑なロジックを組んでいると、そもそも「全部作ってから動かしてみる」のではなく、部分的に作りこんで動作を確認してから次の部分に、という作り方をするのが一般的である。また、今回は最終的に外部に出てきている信号で成否を判断したが、内部ロジックの検証などでは外部の信号が使えない場合も珍しくない。

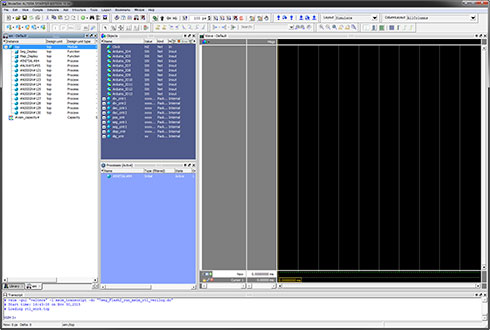

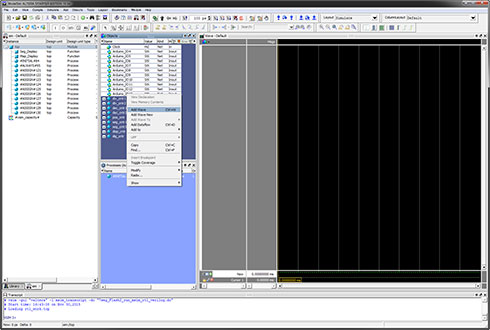

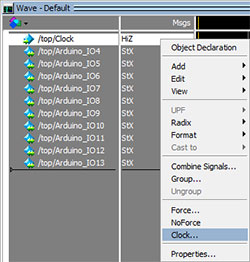

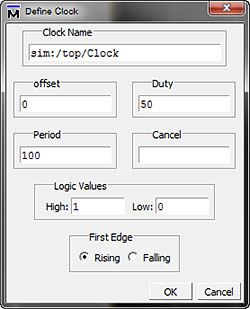

こうした場合に利用できるのがシミュレーションである。幸いにもQuartus IIには無償版ながらシミュレーションツールが利用可能である。起動するとこんな画面になるので(Photo04、05)、作業中のプロジェクトを選ぶと、実際にデザインの中身が見える(Photo06)。今回はClock信号とArduino_IO4〜13を表示させてみる(Photo07)。ただこの状態だと/top/ClockがHi-Z状態で進まないので、ここにClock信号を入力する(Photo08、09)。

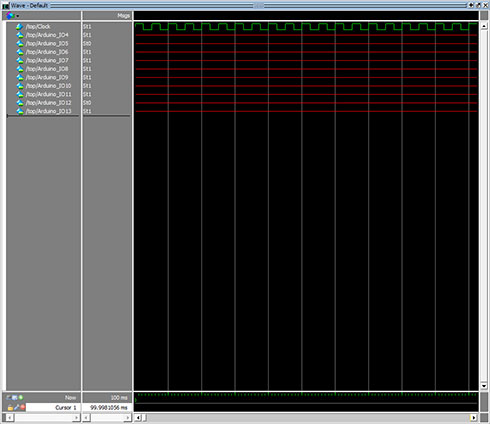

ついでにメニューから「Simulate」→「Runtime Option」を選んで、1回に実行される時間を100psから100msまで増やしておく。これが終わったら、メニューの「Simulate」 → 「Run」 → 「Run 100」を選ぶと、Waveがこんな風になるはずだ(Photo10)。

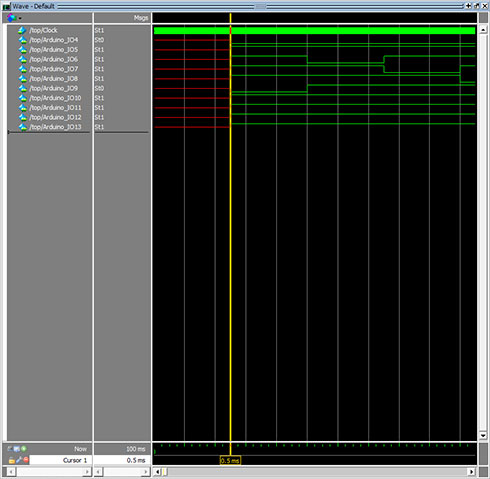

このままだとちょっと見にくいので、上の縮小ボタンなどを使って、先頭から2msほどを表示させたのがこちら(Photo11)。カーソルの位置からも分かる通り、キチンと0.5msごとに出力信号が変化していることが分かる。今回は省くが内部レジスタやWireの値などを同様に表示することも可能であり、シミュレーション上も正しく動作することが検証された形だ。

次回はちょっと別のことをご紹介したい。

「MAX 10 FPGA 評価キット」プレゼント

| 募集要項 | |

|---|---|

| 応募期間 | 2015年12月11日(金) 〜 2016年1月15日(金) |

| 応募条件 | アイティメディアIDの登録ユーザー |

| 当選発表 | 当選された方には配送先の住所をお聞きするために登録メールアドレスにEメールをお送りします。配送先住所をご記入の上ご返信いただいた方にプレゼントをお送りします。 |

| 当選無効 | Eメールのご返信は7日以内とさせていただきます。8日目以降にご返信いただいても、当選は無効とさせていただきます。 |

| 応募上の諸注意 | ・キャンペーン期間中にアイティメディアIDの登録を削除された方は対象に含まれません ・当選者の権利は譲渡・換金・変更することはできません ・厳正な抽選の上、当選者の方へ賞品を発送、もしくはご連絡を差し上げます。なお、賞品のお届け先は日本国内に限らせていただきます。抽選と発送は2016年1月下旬〜2016年2月下旬の予定です ・お預かりした個人情報は、アイティメディアIDの利用規約とアイティメディア株式会社の 「プライバシーポリシー」に基づいて厳重にお取り扱いいたします ・住所・電話番号などが不明確な場合や、転居による住所変更や電話番号変更など、何らかの理由により賞品がお届けできない場合は当選を無効とさせていただきます ・ご応募はお一人さま1回限りとさせていただきます。2回以上ご応募された方は、抽選対象外とさせていただきますのでご了承下さい。 |

※アイティメディアIDにご登録済みの方でも、追加の情報登録をお願いする場合があります。ご了承ください。

関連記事

FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 「MAX 10 FPGA」のテスト環境を構築する

「MAX 10 FPGA」のテスト環境を構築する

今回から実際に「MAX 10 FPGA評価キット」を利用しての開発に着手する。まずは環境構築だ。キット以外に必要なモノもあるので注意して欲しい。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。 いまさら聞けない FPGA入門

いまさら聞けない FPGA入門

あなたは、人に「FPGA」を正しく説明できるだろうか? いまや常識となりつつあるFPGAについて、あらためてその概念から仕組み、最新動向までを解説する。(編集部)

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- CPLD級のプログラマブルロジックを統合したマイコンを発表

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 安全認証対応エッジAIシステムの高度化へ向けNVIDIAとの協業を拡大

コーナーリンク