デジタルデバッグにはなぜロジアナ? 仕組みと歴史:いまさら聞けないロジック・アナライザ入門(1)(2/2 ページ)

ロジック・アナライザの歴史

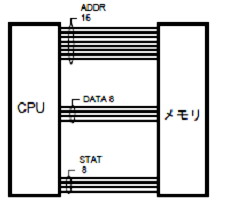

1970年代初めまでは、デジタル製品のデバッグ時にはオシロスコープが使われていました。しかしながらCPUのアドレスやデータのビット幅が8→16→32と増えるにつれ、観測すべき信号数が増加し、2〜4チャネル入力のオシロスコープでは対応が困難になってきました(図3)。

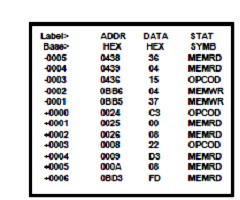

また、ソフトウェアの開発時に、プログラムが特定の処理を行ったところや、特定のアドレスにアクセスしたときの状態を確認したいというニーズも出てきました。つまり、信号を単なる波形としてではなく、8ビットや16ビット幅のバスのデータとして読み取り、そのデータが示す意味を解釈して表示する必要性が高まりました(図4)。

これらのニーズに応えて、現在のロジック・アナライザの前身となるステートアナライザやタイミングアナライザが登場しました。

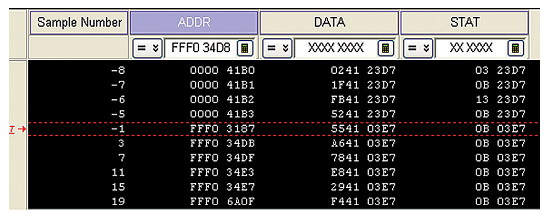

ステートアナライザは、外部クロック信号に同期して信号をサンプリングします。例えばCPUのアドレスバスやデータバス上の信号を、システムクロックに同期してサンプリングすることで、システムが処理している信号と同じものを観測することができます。また、アドレスバスやデータバスのイベントでトリガを掛け、リスト表示でアドレスやデータを分かりやすく表示することができます(図5)。このため主にソフトウェアの解析に活用されました。

タイミングアナライザは、システムクロックとは非同期に信号をサンプリングし、波形として表示します。アナライザの内部クロックにより高速サンプリングを行うことで、多数の信号の細かなタイミングの違いを確認することができます(図6)。このため主にハードウェアの解析に活用されました。

その後システムの複雑化が進むと、不具合の原因がハードウェアとソフトウェアのどちらにあるのかという切り分けが重要になりました。そこで、ステート解析とタイミング解析の両方の機能を持ったロジック・アナライザが1980年代に登場しました。現在販売されている多くのロジック・アナライザは、ステート解析とタイミング解析の両方の機能を備えています。

ロジック・アナライザの仕組み

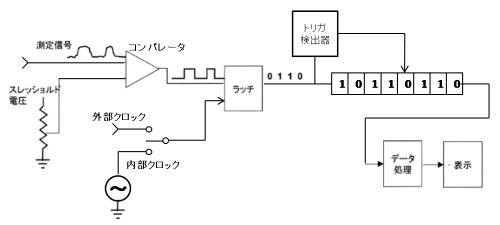

図7にロジック・アナライザのブロック図を示します。

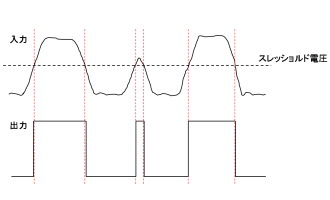

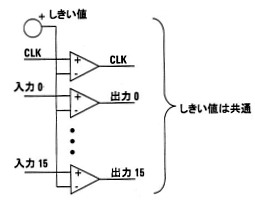

最初に、ロジック・アナライザは入力された信号が1か0かの判別を行います。これにはコンパレータが使用されます。コンパレータは入力信号の電圧とスレッショルド(しきい値)電圧を比較し、信号の電圧の方が高ければ1、低ければ0と解釈します(図8)。スレッショルド(しきい値)電圧はユーザーが任意の値に設定可能で、各種信号規格のレベルに合わせた設定が可能です。このようなシンプルな構成のため、多チャネル化が容易です(図9)。

コンパレータの出力は、サンプリング・クロックのタイミングでラッチされます。サンプリング・クロックとして外部クロックまたは内部クロックが選択でき、これによりロジック・アナライザの動作モードが決まります。それぞれの動作モードの違いは表1のとおりです。詳細は次回以降でご紹介します。

表1 ステート解析モードとタイミング解析モードの比較

| ステート解析 | タイミング解析 | |

|---|---|---|

| サンプリング方式 | 同期 | 非同期 |

| サンプリング・クロック | 外部クロック | 内部クロック |

| データ表示形式 | リスト表示 | 波形表示 |

サンプリングされた信号はメモリに保存されます。メモリがいっぱいになると古いデータから順番に破棄され新しいデータが上書きされます。トリガ回路は、ユーザーが指定したデータパターンなどのトリガイベントを検出し、ロジック・アナライザのサンプリング動作を停止します。その後メモリ内のデータが処理され画面に表示されます。

次回は、ステートとタイミングそれぞれの解析モードについて、オシロスコープやミックスドシグナルオシロスコープとの比較を交えながら、もう少し詳しく説明します。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク

図3 ロジック回路の例

図3 ロジック回路の例 図4 アドレスバス、データバスの表示例

図4 アドレスバス、データバスの表示例 図5 ステート解析の例

図5 ステート解析の例 図6 タイミング解析の例(赤枠内:細かなタイミングの違い)

図6 タイミング解析の例(赤枠内:細かなタイミングの違い) 図7 ロジック・アナライザのブロック図

図7 ロジック・アナライザのブロック図 図8 コンパレータの動作

図8 コンパレータの動作 図9 ロジック・アナライザの入力部

図9 ロジック・アナライザの入力部