実は限られた得意領域も実現したら絶大な影響力、国内の量子コンピュータ開発:量子コンピュータ(1/2 ページ)

産業総合研究所(産総研)は、現在進めている量子コンピュータと量子アニーリングマシンに関する研究開発の状況やつくばセンター(茨城県つくば市)の研究施設を報道陣に公開した。

産業技術総合研究所(産総研)は2022年9月30日、現在進めている量子コンピュータと量子アニーリングマシンに関する研究開発の状況やつくばセンター(茨城県つくば市)の研究施設を報道陣に公開した。

国内初の量子アニーリングマシンを開発

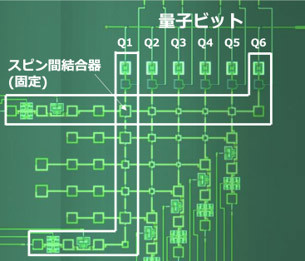

産総研では、新エネルギー・産業技術総合開発機構(NEDO)の「IoT推進のための横断技術開発事業」において、日立製作所らとともに2016年度から量子アニーリングマシンの研究開発に取り組み、2021年には横浜国立大学と連携して独自のアーキテクチャに基づく6量子ビットの超電導量子アニーリングマシンの開発に日本で初めて成功した。

産総研が提唱したアーキテクチャであるASAC(Application Specific Annealing Computation)は、特定の組み合わせ最適化問題に特化しているのが特徴だ。通常の量子アニーリングマシンは、あらゆる組み合わせ最適化問題に対応したアーキテクチャを採用している。そのため、大規模な問題を解くためには必要な量子ビットの数も膨れ上がる。

ASACでは従来方式に比べて1桁程度少ない量子ビット数で、組み合わせ最適化問題を解くことが可能となる。大規模な問題になっても、量子ビット数の増大が抑えられる。その時作られたチップ「AQUA1.1」の材料はニオブで、量子ビットはリング構造をした超電導磁束量子ビットで集積化した。

現在、NEDOの委託事業「量子計算及びイジング計算システムの統合型研究開発」(2020年度〜最長2027年度)として、NECらとともに引き続き量子アニーリングマシン、量子コンピュータの研究開発を行っている。

ダークホースの超電導パラメトロン

NECが中心に進めているのが、超電導パラメトロンを利用した超電導量子アニーリングマシンの開発だ。NECは、ゲート型量子コンピュータに用いる超電導量子ビットを1999年に開発した。この技術を応用し、2022年に4量子ビットの量子アニーリングマシンの開発に成功している。超電導パラメトロンは量子重ね合わせ状態の位相が保たれる量子コヒーレンス性能に優れている他、モジュール構造と3次元実装の採用により、大規模集積化が容易とされる。

「超電導パラメトロンを用いた量子アニーリングマシンはビット反転エラーがほとんどなく、誤りを修正するために必要な量子ビット数を劇的に少なくすることができ、少ない量子ビット数で大規模な問題を解きうるかもしれないという期待がある」(産総研 新原理コンピューティング研究センター 川畑史郎氏)

組み合わせ最適化問題に特化した量子アニーリングマシンは、2011年にカナダのD-Wave Systemsが商用化に成功し、2020年には5600量子ビット級の商用機を販売している。しかし、社会実装のためには100万量子ビット級の大規模集積化が必要とされる。また、幅広い問題に対応可能で汎用性のある量子コンピュータは2021年にIBMが128量子ビットの量子コンピュータを開発しているが、100万量子ビット級にたどり着くには20〜30年掛かると見られている。

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- 非公開化から始まる「富士ソフト Gen.2」、AI×IT×OTの融合が勝ち筋に

- 空前のAIブーム!「猫も杓子もAI」な現状は今後も続くのか?【前編】

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- 日立と日立ハイテクが独自エッジAI半導体を開発、先端GPU比で処理効率10倍以上

- 消費電流20nAと1.2V駆動を両立した磁気スイッチ用AMRセンサー

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- 40台超のロボットを統合管理する自律運用システムが本格稼働

コーナーリンク

産総研 新原理コンピューティング研究センター 川畑氏

産総研 新原理コンピューティング研究センター 川畑氏