第22回 オンチップ電源:前田真一の最新実装技術あれこれ塾(2/3 ページ)

例えば、2012年の世界のスーパーコンピュータTop500ではインテル社のXeonが半数近くに使われています。ノートPCだけではなく、これらのサーバやスーパーコンピュータでも省エネは非常に大きな性能要素になっています。

サーバでは電力料金に値上げや世の中の省エネの流れに乗って、システムの消費電力が大きな注目を集めています。CPUの消費電力が減れば、当然、発熱も少なくなり、空調設備のコスト、電力も大幅に減り、電源設備と合わせ、大きなコスト削減になります。

スーパーコンピュータでは電源はもっと大きな問題となります。

例えば、スーパーコンピュータ『京』(図5)では、2012年11月TOP500リストのベンチマーク計測時の電力使用量は、約12.66MWでした(富士通のHPより)。

2012年11月に『京』を抜いて性能トップと2位になったシステムの消費電力は『京』の2/3程度です。

TOP10の中では最も電力効率はよくありません(表1)。

しかしこれでも『京』は、TOP500の中ではまだ電力効率は良い方なのです。

このままでは、スーパーコンピュータを作るためにはまず発電所から作らなければならなくなります。このため、スーパーコンピュータでも性能/消費電力が大きく注目され、性能指針として取り上げられています。

このように、スーパーコンピュータからノートPCまで、CPUの消費電力が大きな問題になっています。

インテル社が新しいCPUアーキテクチャで消費電力問題に本質から向き合ったのはこのような背景からです。

4. Haswellの消費電力問題対策

ここで、Haswellの消費電力はCPUが動作していない時の待機電力を現在のIvy Bridgeの1/20、トータルの消費電力を1/2にするといわれています。

いきなり待機電力を現在の1/20にするといっても、これは簡単ではありません。現在のIvy Bridgeでも現在の技術で可能な限り、消費電力を低減するための努力はしています。

このため、多くの新しい考えや技術の改善を行い、それらを一つ一つ積み上げて消費電力の低減を行っています。

その中でも実装にとって特に気になる機能に、次のような記述があります。“……Haswell has on-die voltage regulator……”。LSI内部にレギュレータ回路を実装したものをオンチップ・レギュレータと呼び、ここ数年、研究されてきています。インテル社でも、数年前からこの技術を研究していて、その成果などを発表していました。

そしてついにHaswellにこの機能が実装されるようになったものです。

まだ、Haswellにどのような回路が実装されるのか、どの程度の容量の電源がいくつ実装かされるなど、発表はされていませんが、これが電源の新しい時代を迎える第一歩になることは間違えないでしょう。

5. オンチップ・レギュレータ

オンチップ・レギュレータには大きく3つのメリットがあります。しかし、技術的な困難のため、なかなか実際のLSIには実装することができません。

まず第1のメリットは、基板実装面積の縮小とコストダウンです。現在は、LSI電源の多様化が進み、ことなるLSIではことなる電源電圧を使う場合が多くなってきています。さらに、他のICとのデータ授受や、標準インタフェースのため、1つのLSIでも多くの電圧を使っています。

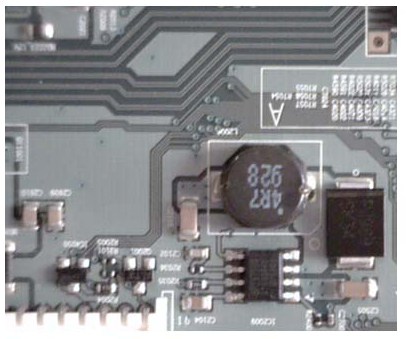

現在は、基板上でおのおののLSIの近くに電源回路を組み、おのおののLSIに供給しています。このため、基板上には多くの電源回路が存在し、電源回路のコストと、基板上で電源回路が占める領域は無視できません(図6)。

ICがおのおの、自分で使用する電圧の電源を自分で作成できるようになれば、基板面積と電源回路用の部品コストを大幅に削減できます。

第2のメリットは、電源変動への対策です。

SSOノイズとして知られるLSIの電源変動が大きな問題となったのは、2つの原因があります。LSI回路の大規模化による消費電力の増大による、変動の増大と信号の高速化による、消費電力変動の高速化です。

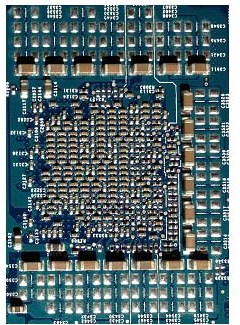

LSIの消費電力増大は、そのまま消費電力変動の増大になり、対策部品である、バイパスコンデンサの増大を招きました(図7)。

LSIの消費電力変動の高速化は電源変動の高速化を招き、電源供給ライン(PDN)のL成分の低下や、バイパスコンデンサ自身のL成分の低減を要求しました。

これらの理由から、SSOノイズの変動を抑えるため、PI(Power Integrity)解析という新しい考えが生まれ、PDNのインピーダンス解析や基板の電源/GNDプレーンの設計や、バイパスコンデンサの配置、数などの決定に細心の注意を払う必要が出てきました。

これら電源系統の解析、設計には高価な専用ツールと多くのコスト、時間がかかっています。さらに多くのバイパスコンデンサの配置や、プレーン層の追加などにより、基板や部品のコストに多大な費用がかかっています。

また、電源のノイズは、単に信号ノイズやタイミングノイズとして信号の伝送品質を下げるだけではなく、電磁放射(EMI)ノイズの大きな原因となります。

現在の電子機器ではEMI対策には大きなコストが費やされています(図8)。

基板上に電源を配置すると、基板配線やビアがもつL成分のため、LSI電源の変動を完全に抑えることはできません。このため、現在は、よりLSIに近いパッケージ上にコンデンサを載せたり、さらにはLSI内部にまでコンデンサを作り込んだりして対応しています。

LSI内部に電源装置をもたせることができれば、配線やビアのもつL成分の影響がなくなり、電源電圧安定化のためには理想的な状態になります。

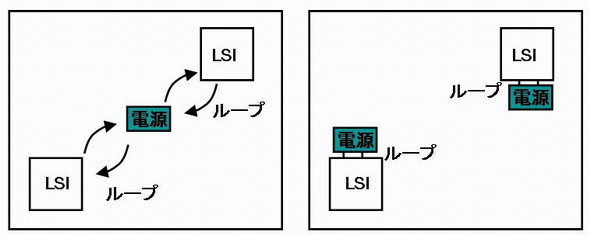

さらに、LSI内部の小さな回路ブロックごとに電源回路をもつようにすれば、おのおのの電源回路に対する消費電力の変化は小さくなるので、さらにLSIの各回路の電源電圧は安定します(図9)。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- なぜオムロンは農業の“作業”ではなく“判断”の自動化を目指すのか

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

コーナーリンク

図5 京(富士通)

図5 京(富士通) 表1 スーパーコンピュータTop10(2012)(Top 50 Super Computer)

表1 スーパーコンピュータTop10(2012)(Top 50 Super Computer) 図6 基板上の電源回路

図6 基板上の電源回路 図7 大量のバイパスコンデンサ

図7 大量のバイパスコンデンサ 図8 EMI対策部品(Nintendo)

図8 EMI対策部品(Nintendo) 図9 ループが小さいとレスポンスが速い

図9 ループが小さいとレスポンスが速い