大衆車にも求められる「予防安全」:普及の鍵は、ミリ波レーダーの低価格化(7/7 ページ)

CMOSでの開発事例も

上述したように、SiGeプロセスを用いた車載ミリ波レーダー送受信ICは、すでに実用化の段階に入っている。そして、SiGeプロセスを上回る集積度を実現可能なCMOSプロセスを用いて送受信ICを開発する動きも始まっている。

東芝は、65nmのCMOSプロセスを用いて、車載ミリ波レーダー用の周波数シンセサイザICを開発した。同ICを用いることで、現行の車載ミリ波レーダーと比べて、周波数シンセサイザ回路にかかるコストを約1/4に低減できるとしている。

現行の車載ミリ波レーダーが高コストである要因としては、GaAsベースの個別部品を用いた送受信回路以外に、車載ミリ波レーダーで一般的な FMCW(Frequency Modulation Continuous Wave:周波数変調連続波)方式の変調に用いるDDFS(Direct Digital Frequency Synthesizer) ICなどが高価であることも挙げられている。

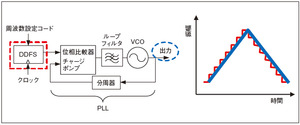

FMCW方式を採用する一般的な車載ミリ波レーダーの周波数シンセサイザ回路では、DDFS ICが、入力される周波数設定コードと基準クロックを基に、基準周波数信号(三角波)をアナログ信号としてPLLに出力する。ここでいう周波数設定コードとは、理想的な三角波を生成するための入力デジタルコードのことである。そして、この基準周波数信号を制御信号として用い、PLL内部にあるVCO(電圧制御発振器)でミリ波信号を出力する(図4)。このようなフィードバック制御を利用したPLL構成を用いる理由は、VCOは制御電圧に対して非線形な出力周波数信号を生成する(三角波を入力しても、直線的に周波数が変化する出力信号が得られない)ので、その非線形特性を補償するためである。

ただし、DDFS ICとPLLを利用した周波数シンセサイザ回路にも1つ問題がある。DDFSは入力デジタルコードに応じてアナログ信号を出力する方式であるため、生成する基準周波数信号の三角波は、階段状の波形となる(一般的なD-Aコンバータの出力を思い浮かべればわかりやすい)。この階段状の波形は、PLLのフィルタ機能によって滑らかになるので、条件によっては問題にはならない。しかし、車載ミリ波レーダーによって検出する相対速度の分解能を高めたい場合には、基準周波数信号の周期を長くする必要がある。周期を長くした場合、DDFS ICの分解能が低いと、理想的な三角波と比べて階段状の波形の形状が粗くなってしまい、最終的に得られるミリ波の精度が劣化してしまう。この問題を回避するには、高精度なDDFS ICが必要になり、コスト面で大きな問題となってしまうのである。

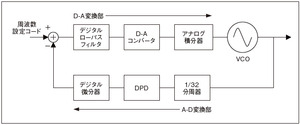

東芝が新たに開発した周波数シンセサイザICは、従来はDDFS ICからのアナログ出力を処理するために純粋なアナログ回路で構成していたPLLに替えて、デジタル回路とアナログ回路を組み合わせた新たなPLL(ミックスモードPLL)を搭載している。図5は、このミックスモードPLLを搭載した周波数シンセサイザの回路構成を示したものである。

この回路の動作を大まかに説明すると、次のようになる。ミックスモードPLLの回路は、VCOで発振したアナログ信号(の位相情報)をデジタル信号(デジタルコード)に変換して処理するA-D変換部と、そのデジタルコードと周波数設定コードの差分をアナログ信号に変換してVCOに出力するD-A変換部に分かれる。A-D変換部では、VCOで発振した77GHz帯のミリ波信号を1/32に分周してから、デジタル位相検出器(DPD)によって位相(周波数)情報を表すデジタルコードに変換する。次に、D-A変換部では、周波数設定コードとA-D変換部で得たデジタルコードとの差分をD-Aコンバータでアナログ信号に変換し、さらにアナログ積分器によって波形を滑らかにした三角波を出力する。この三角波を電圧制御信号としてVCOに入力することにより、 77GHz帯のミリ波を出力する。

このミックスモードPLLの最大の特徴は、A-D変換部で発生する誤差を、D-A変換部で取り除く仕組みにある。DPDにおいて位相情報を得る際には、アナログ情報からデジタル情報を得るので、必ず誤差が生じる。この誤差は、DPDの後段のデジタル微分器における処理により高周波領域にシフトする。この高周波領域にシフトされた誤差は、D-A変換部のデジタルローパスフィルタによって容易に取り除くことができる。東芝 研究開発センター ワイヤレスシステムラボラトリーの櫻井宏樹氏は、「従来のミリ波レーダーのアナログPLLでは、アナログのローパスフィルタによって高周波領域の誤差を取り除いていたが、低周波領域の誤差は取り除くことができなかった。この低周波領域の誤差を小さくするために、高精度のDDFS ICを用いたり、数百MHzものオーバーサンプリングを行ったりしていた。ミックスモードPLLを用いることにより、それら高コストの回路を用いた場合と同等の性能を達成できる。もちろん、部品点数も削減できるので、ミリ波レーダーユニットの小型化にも貢献できるだろう」と説明する。

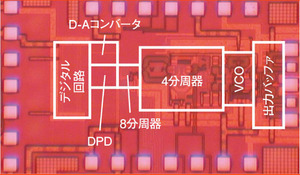

東芝は、この周波数シンセサイザICを65nmのCMOSプロセスで試作している(写真3)。チップのサイズは1.7mm×1.0mm。電源電圧は 1.2V、消費電力は152mWとなっている。同チップを用いた77GHz帯ミリ波レーダーの性能は、変調帯域が1.5GHz(距離分解能で10cmに相当)、変調周期が10ms(相対速度分解能で1.4km/hに相当)、出力する三角波の線形性の平均誤差が0.04%以内だった。これらの値は、高精度の DDFS ICを用いた場合とほぼ同等であるという。

櫻井氏は、「当社は、2009年6月に、90nmのCMOSプロセスを用いて送受信回路とPLLを集積した1チップ送受信ICを発表している。これと今回の周波数シンセサイザICの開発成果を組み合わせれば、すべてをCMOSプロセスで構成した、より安価な車載ミリ波レーダーを実現できるようになる。 2015年〜2016年にも実用化できるように、さらなる研究開発を進めていきたい」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.

モビリティの記事ランキング

- 「EVはオワコン」なのか? 消費者の半数がガソリン車を選択、専門家の見解は

- ジヤトコのドライブユニット「GLIDE AXCEL」を搭載した電動アシスト自転車が誕生

- ヒューマノイドの“始祖”ホンダP2――「不可能」に挑んだ自立二足歩行の歩み

- トヨタが研究開発拠点「TTC-S」を公開、「走る・壊す・直す」を一気通貫で行う

- ホンダの小型EV「Super-ONE」は日常の移動に刺激を与える 2026年5月下旬に販売へ

- デンソーとロームの協業は「新たなステージ」へ、株式取得提案は取り下げ

- 欧州に迫り来るPHEV淘汰の危機

- 小型船舶でも進む操船のシステム化、環境対応も浸透――ボートショー2026レポート

- 中東情勢が国内製造業に与える減益影響じわり、日立200億円デンソー450億円

- 日本初、極超音速実験機を用いたマッハ5燃焼実験に成功

コーナーリンク