アルテラ「Stratix 10」にHBM2 DRAM統合製品、メモリ帯域幅10倍に:FPGA

米Alteraが同社SoC FPGA「Stratix 10 FPGA & SoC 」にSK Hynixの広帯域メモリを統合した「ヘテロジニアス SiP (System-in-Package)デバイス」を発表した。このメモリ統合型Stratix 10は2017年に出荷される。

米Alteraは2015年11月10日(現地時間)、SK Hynixの広帯域メモリと同社ハイエンドSoC(System on Chip)FPGA「Stratix 10 FPGA & SoC 」(以下、Stratix 10)を統合した「ヘテロジニアス SiP (System-in-Package)デバイス」を発表した。このメモリ統合型Stratix 10は2017年に出荷される予定だ。

データセンターや超高速ネットワーキングなど、高いメモリ帯域幅を求める要件に対応するために開発されたデバイスで、パッケージにSK HynixのHBM2(High Bandwidth Memory 2)を統合する。メモリをFPGAダイに近づけて配置することから配線長の短縮が可能となり、メモリの広帯域化と低消費電力化の双方を実現。既存製品の10倍にも及ぶ帯域幅を実現するとしている。

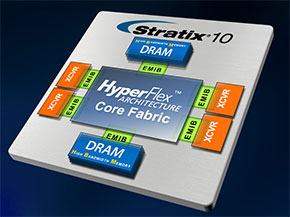

Stratix 10はCPUコアにARM Cortex-A53を採用、インテルの14ナノメートルトライゲートプロセスにて製造されるSoC FPGA。全ての配線セグメントにレジスタを配置する「HyperFlex」アーキテクチャの採用と、14nmトライゲートプロセスの導入により、「従来製品比2倍のコアパフォーマンスと最大70%の消費電力削減を可能にした」(同社)とする。

インテルの2.5D実装技術「EMIB(Embedded Multi-die Interconnect Bridge)」を用い、各種のトランシーバを「TILE」とよぶブロックとして実装するヘテロジニアスインテグレーション「3D SiP」も導入されており、HBM2メモリの統合もEMIBの採用により実現したものだ。Stratix 10は2016年に出荷開始される予定となっている。

関連記事

- FPGAでのLチカをVerilog HDLで理解する

- 課題解決をFPGAで――FPGA初心者歓迎の日本アルテラ

- アルテラ、14nm世代に向けた開発環境「Quartus Prime」

- 「Stratix 10」詳細が発表、“どこでもレジスタ”で性能2倍

- インテルがFPGA大手アルテラを買収

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

組み込み開発の記事ランキング

- 動かぬ検証機「SEIMEI」に純国産ヒューマノイド開発に向けたKyoHAの覚悟を見た

- ソフトバンクが堺にギガファクトリー、国産の燃えない水電池を2027年度に量産へ

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ソニーのフィジカルAIが卓球の一流選手に勝利、自律システム「Ace」の研究成果

- 万博を終えたアンドロイドたちの「新たな住まい」 長谷工が描く人と技術の交差点

- CPLD級のプログラマブルロジックを統合したマイコンを発表

- 複数のFPGAファミリーの製品ライフサイクルサポートを2045年まで延長

- AIが下半身の動きをサポート 韓国発のウェアラブルロボット「WIM S」が日本に上陸

- パワーデバイスの損失や温度上昇を数秒で検証できる高速シミュレーターを公開

- 安全認証対応エッジAIシステムの高度化へ向けNVIDIAとの協業を拡大

コーナーリンク