第13回 TSVが量産技術へ〜Wide I/O規格:前田真一の最新実装技術あれこれ塾(2/3 ページ)

3. 機械的仕様の概要

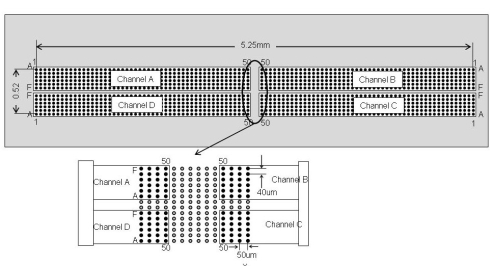

規格では、メモリチップは最大4枚になっていますが、インタフェース的にも300パッドのチャンネルと呼ばれるブロックが4チャンネル存在します。

Wide I/Oメモリでは、1チャンネルには6列50行の300パッドが40μm×50μmピッチで配置されます。

これが2×2の4チャンネル配置され、合計1200パッドとなります(図3)。

このため、パッドの占有面積は(5.25+α)×(0.52+α)mmとなります(αはパッドの径)。

メモリのチップサイズはパッドレイアウト幅の0.52mmよりは大きいので、メモリ外形はさらに大きくなるでしょうが、現在は、パッケージサイズは定義さえていません。

4. 電気的仕様の概要

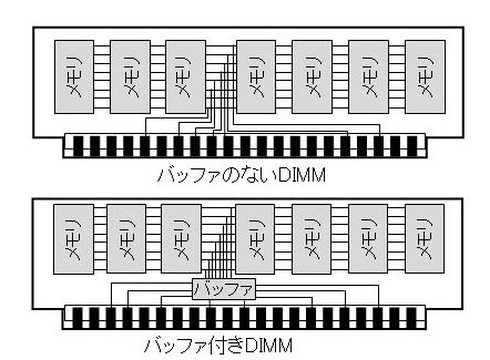

DIMMなどのように、コントローラICに複数のメモリを接続する場合には直接メモリを接続する場合とバッファを介して接続する場合があります(図4)。

JEDECの規格としては、DDR規格とかLPDDR企画などのメモリ単体の規格のほか、DIMMの規格も制定しています。DIMM規格では、バッファのあるDIMM規格とバッファのないDIMM規格を定めています。

しかし、今回のWide I/Oメモリでは部品としては、必ずバッファチップを必要とし、メモリチップをその上に3D実装する構造をとっています。このため、Wide I/Oの電気特性規格の多くはバッファチップの電気特性になっています。

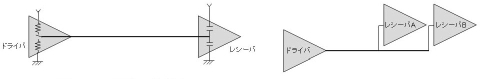

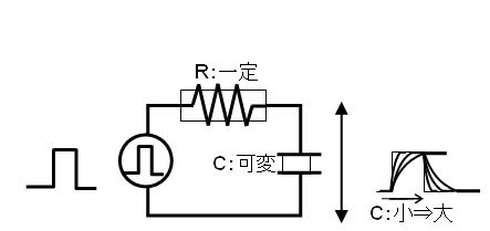

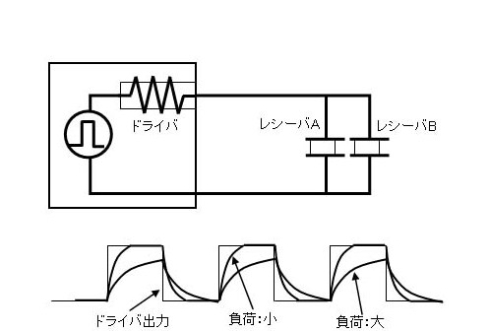

メモリインタフェースのCMOS回路では、レシーバの入力容量の大きさが重要です。CMOS回路では、レシーバの入力インピーダンスは高いので、ドライバの出力インピーダンスとレシーバの入力容量で積分回路を形成します(図5)。

図6の回路のCで示される、レシーバの入力容量が大きいと、信号波形が鈍り、信号の高速伝送ができなくなります(図6)。

もし、バッファがなく3D実装された複数のメモリチップがコントローラICに直接、接続された場合、チップの数が増えるほど入力容量が並列接続され、信号が低速になってしまいます(図7)。

このため、複数のメモリチップを3D実装する場合には、複数のメモリチップを直接基板配線に接続しないで、低容量のバッファを介して基板配線に接続する必要があります。

メモリパッケージ内のバッファとメモリチップ間の接続では配線が非常に短いため、複数のチップを接続して容量が大きくなっても、信号の高速伝送が可能です。

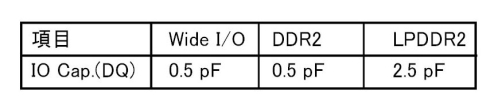

バッファがあるためWide I/Oの規格では、メモリチップが1つだけ使われているDDR2規格やLPDDR2規格と同じ入力容量になっています(表1)。

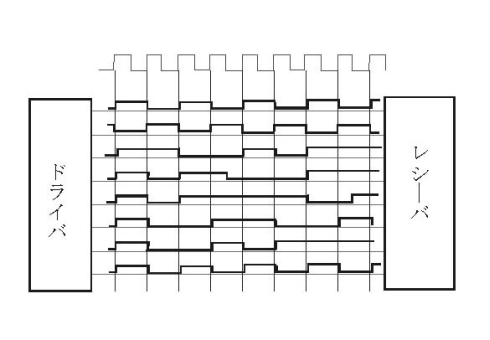

メモリバスのような並列データ転送方式ではデータ間のタイミングの同期が最も重要です(図8)。Wide I/Oメモリではデータ転送速度を遅くして同期時間に余裕をもたせました。

Copyright © ITmedia, Inc. All Rights Reserved.

Factory Automationの記事ランキング

- 日本が再び世界をリードするための、“シン”モノづくりの世界

- 自動車工場で聞こえるのに、食品工場では聞こえない音〜工場の主人公は誰か

- 「自動車以外は全て好調」、四半期受注過去最高のDMG森精機が通期予想上方修正

- エンジニアリング業務を自律実行、シーメンスが産業AIを新たな段階に

- マグネットで触れるだけ、振動値を5秒で判定する回転機振動チェッカー

- 「ロボット大国」日本の逆襲、地道なモノづくりが世界を動かす交渉力に

- 猛暑に備えて

- 工場の主人公は誰なのかという問いかけ、元トヨタ生技が見た食品工場のなぜ

- ヒューマノイド中核部品がハノーバーメッセ技術賞、“脱自動車”のシェフラー開発

- 防衛事業の生産体制強化、ソナーなど水中音響センサーの新生産棟を建設

コーナーリンク

図4 バッファのある場合と無い場合

図4 バッファのある場合と無い場合

図6 積分回路

図6 積分回路 図7 負荷を並列接続すると信号は遅くなる

図7 負荷を並列接続すると信号は遅くなる 表1 DDRメモリの入力容量規格

表1 DDRメモリの入力容量規格 図8 並列バスでは信号の同期が重要

図8 並列バスでは信号の同期が重要