TSMCВ™ОYСНМ§УаВ…Х]ЙњЧpГЙГCГУН\ТzБAМoОYП»ВћОЯРҐСгФЉУ±СћЛZПpОxЙЗВ≈БFFAГjГЕБ[ГX

МoНѕОYЛ∆П»ВЌ2021ФN5МО31УъБAБuГ|ГXГg5GПоХсТ РMГVГXГeГАКоФ’Л≠ЙїМ§ЛЖКJФ≠ОЦЛ∆БvВћБuРжТ[ФЉУ±СћРїСҐЛZПpВћКJФ≠БiПХРђБjБv…®ƒВйОјО{О“В∆ВµВƒБAБuНВРЂФ\ГRГУГsГЕБ[ГeГBГУГOМьВѓОјСХЛZПpБvВ…К÷ВЈВйTSMC»«БA5МПВћНћСрВрМИТиµšБB

Б@МoНѕОYЛ∆П»ВЌ2021ФN5МО31УъБAБuГ|ГXГg5GПоХсТ РMГVГXГeГАКоФ’Л≠ЙїМ§ЛЖКJФ≠ОЦЛ∆БvВћБuРжТ[ФЉУ±СћРїСҐЛZПpВћКJФ≠БiПХРђБjБv…®ƒВйОјО{О“В∆ВµВƒБAБuНВРЂФ\ГRГУГsГЕБ[ГeГBГУГOМьВѓОјСХЛZПpБvВ…К÷ВЈВйTSMC»«БA5МПВћНћСрВрМИТиµšБB

TSMCВ™ОYСНМ§ВћГNГКБ[ГУГЛБ[ГАУаВ…ГvГНГZГXГЙГCГУВрН\Тz

Б@БuГ|ГXГg5GПоХсТ РMГVГXГeГАКоФ’Л≠ЙїМ§ЛЖКJФ≠ОЦЛ∆БvВЌБA5GЛZПpВрГxБ[ГXВ∆ВµБAВ≥ВзВ…ТіТбТxЙДВвСљРФУѓОЮЏѱ»«žЛ@Ф\В™Л≠ЙїВ≥ВкВљБuГ|ГXГg5GБvВ™Н°МгБAНHПкВвΩӁΑ»«њЧlВ»ОYЛ∆ЧpУrВ≈КИЧpВ™М©НЮВ№ВкВƒВҐВйВ±В∆В©ВзБAВ±ВкВзВћТЖКjВ∆В»ВйЛZПpВрКJФ≠ВЈВйВ±В∆В≈БAРїСҐКоФ’Л≠ЙїВрЦЏОwВЈВаВћВ≈В†ВйБBГ|ГXГg5GПоХсТ РMГVГXГeГАВвК÷ШAВЈВйФЉУ±СћЛZПpВћКJФ≠ВрРiВяВйВ∆В∆ВаВ…БAГ|ГXГg5GВ≈ХKЧvВ»ФЉУ±СћВрПЂЧИУIВ…НСУаВ≈РїСҐВ≈ВЂВйЛZПpВрКmХџВЈВйВљВяВ…БAРжТ[ФЉУ±СћВћРїСҐЛZПpКJФ≠В…ОжВиСgВёБB

TSMCГWГГГpГУ3DICМ§ЛЖКJФ≠ГZГУГ^Б[В™ГvГНГZГXГЙГCГУВрН\ТzВЈВйОYЛ∆ЛZПpСННЗМ§ЛЖПКВћГNГКБ[ГУГЛБ[ГАБ@ПoУTБFМoНѕОYЛ∆П»

Б@Н°ЙсНћСрВ™Ф≠Х\В≥ВкВљВћВЌВ±ВћБuРжТ[ФЉУ±СћРїСҐЛZПpВћКJФ≠БvВ…К÷ВЈВйВаВћВЊБBБuНВРЂФ\ГRГУГsГЕБ[ГeГBГУГOМьВѓОјСХЛZПpБvВ∆ВµВƒВЌБATSMCГWГГГpГУ3DICМ§ЛЖКJФ≠ГZГУГ^Б[В™ОуСхµšБB

Б@Л§УѓОјО{КйЛ∆В∆ВµВƒНёЧњГББ[ГJБ[В≈ВЌБAИЃЙїРђБAГCГrГfГУБAJSRБAПЇШaУdНHГ}ГeГКГAГЛГYБAРMЙzЙїКwНHЛ∆БAРVМхУdЛCНHЛ∆БAПZЧFЙїКwБAРѕРЕЙїКwНHЛ∆БAУМЛЮЙЮЙїНHЛ∆БAТЈР£ОYЛ∆БAУъУМУdНHБAУъЦ{УdЛCП…ОqБAХxОmГtГCГЛГАБAОOИдЙїКwВ™ОQЙЅВµВƒВҐВйБBВ№ВљБAСХТuГББ[ГJБ[В∆ВµВƒВЌБAГLБ[ГGГУГXБAО≈ЙYГБГJГgГНГjГNГXБAУЗТ√РїНмПКБAПЇШaУdНHБAГfГBГXГRБAУМГМГGГУГWГjГAГКГУГOБAУъУМУdНHБAУъЧІГnГCГeГNВ™ОQЙЅВЈВйБBСеКwБEМ§ЛЖЛ@К÷В©ВзВЌОYЛ∆ЛZПpСННЗМ§ЛЖПКБAРжТ[ГVГXГeГАЛZПpМ§ЛЖСgНЗБiRaaSБjБAУМЛЮСеКwВ™ОQЙжВЈВйБB

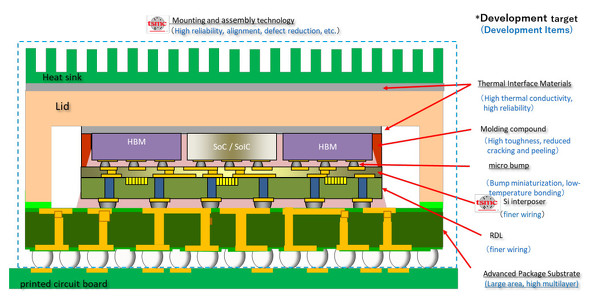

Б@НВРЂФ\ГRГУГsГЕБ[ГeГBГУГOВћОјМїВ…МьВѓВƒБAФЉУ±СћГfГoГCГXВћВ≥ВзВ»ВйПWРѕЙїВ∆НВРЂФ\ЙїВрЙ¬Ф\В∆ВЈВй3DГpГbГPБ[ГWЛZПpВћКmЧІВ…ОжВиСgВёБBКоФ¬ПгОјСХЛZПpВрТЖРSВ…БAРVµ¥ɽНHЛZПpБAКоФ¬НёЧњБAРЏНЗГvГНГZГXБAРVЛKВћРЏНЗЛZПpБAМvС™ЛZПp»«ВрСgВЁНЗВнВєБAКJФ≠ВрРiВяВйБBTSMCГWГГГpГУ3DICМ§ЛЖКJФ≠ГZГУГ^Б[В™БAОYЛ∆ЛZПpСННЗМ§ЛЖПКВћГNГКБ[ГУГЛБ[ГАУаВ…ГvГНГZГXГЙГCГУВрН\ТzВµХ]ЙњБEМЯПЎВрРiВяВƒВҐВ≠БB

3DРѕСwЛZПpВћКJФ≠ВвБAРVВљВ»ГpГbГPБ[ГWХ]ЙњЛZПpВћКJФ≠ВрРДРi

Б@БuГGГbГWГRГУГsГЕБ[ГeГBГУГOМьВѓОјСХЛZПpБvВ∆ВµВƒВЌБAРжТ[ГVГXГeГАЛZПpМ§ЛЖСgНЗБiRaaSБjВ∆Г\ГjБ[ГZГ~ГRГУГ_ГNГ^Г\ГКГЕБ[ГVГЗГУГYВ™ОуСхµšБB

Б@РжТ[ГVГXГeГАЛZПpМ§ЛЖСgНЗВћОЦЛ∆ГeБ[Г}ВЌБAГ_ГCГМГNГgРЏНЗ3DРѕСwЛZПpКJФ≠В≈БACu-CuВћТбЙЈГnГCГuГКГbГhРЏНЗВ…ВжВйWoWБiWafer on WaferБjРЏНЗЛZПpВ∆БACoWБiChip on WaferБjРЏНЗЛZПpВћН\ТzВ∆ВїВћОјСХЙїВ…ОжВиСgВёБBОYЛ∆ЛZПpСННЗМ§ЛЖПКБASCREENГzБ[ГЛГfГBГУГOГXБAГ_ГCГLГУНHЛ∆БAХxОmГtГCГЛГАБAГpГiГ\ГjГbГNГXГ}Б[ГgГtГ@ГNГgГКГ\ГКГЕБ[ГVГЗГУГYБAУМЛЮСеКwВ™Л§УѓОјО{О“В∆ВµВƒОQЙЅВЈВйБB

Б@Г\ГjБ[ГZГ~ГRГУГ_ГNГ^Г\ГКГЕБ[ГVГЗГУГYВћОЦЛ∆ГeБ[Г}ВЌБAГ|ГXГg5GГGГbГWГRГУГsГЕБ[ГeГBГУГOМьВѓФЉУ±СћВћ3DРѕСwЧvСfЛZПpМ§ЛЖКJФ≠ВЊБBГ\ГjБ[В™УЊИ”В∆ВЈВйГCГББ[ГWГZГУГTБ[ВћРѕСwЛZПpВ…В®ВҐВƒБAРѕСwГВГWГЕБ[ГЛВћКоЦ{УЅРЂВ®ВжВ—РMЧКРЂОжУЊВ™Й¬Ф\В∆В»ВйГsГbГ`ГTГCГYЦЏХWВрФNУxВ≤В∆В…РЁТиВµБAГНГoГXГgВ»ФЉУ±СћРїСҐГvГНГZГXВћЧvСfЛZПpВрКmЧІВЈВйБB

Б@БuОјСХЛ§Т КоФ’ЛZПpБvВ∆ВµВƒВЌБAПЇШaУdНHГ}ГeГКГAГЛГYВ∆ПZЧFГxБ[ГNГЙГCГgВ™ОуСхВµВƒВҐВйБB

Б@ПЇШaУdНHГ}ГeГКГAГЛГYВћОЦЛ∆ГeБ[Г}ВЌБAН≈РжТ[ГpГbГPБ[ГWХ]ЙњГvГЙГbГgГtГHБ[ГАСnРђВЊБBКоФ¬БAСХТuБAНёЧњГББ[ГJБ[В…ВжВйГRГУГ\Б[ГVГAГАВ≈БAХ]ЙњГvГЙГbГgГtГHБ[ГАВрРЁТuВµОЯРҐСгФЉУ±СћГpГbГPБ[ГWВћХ]ЙњЛZПpБAКоФ¬БAСХТuБAНёЧњВћКJФ≠ВрНsВ§БBЦ°ВћСfГtГ@ГCГУГeГNГmБAПгСЇНHЛ∆БAЙ`МіРїНмПКБAРVРмБAРVМхУdЛCНHЛ∆БAСеУъЦ{ИуНьБAГfГBГXГRБAУМЛЮЙЮЙїНHЛ∆БATOWAБAГiГ~ГbГNГXБAГpГiГ\ГjГbГNГXГ}Б[ГgГtГ@ГNГgГКБ[Г\ГКГЕБ[ГVГЗГУГYБAГДГ}ГnГНГ{ГeГBГNГXГzБ[ГЛГfГBГУГOГXВ™Л§УѓОјО{КйЛ∆В∆ВµВƒОQЙЅВЈВйБB

Б@ПZЧFГxБ[ГNГЙГCГgВћОЦЛ∆ГeБ[Г}ВЌБAОЯРҐСгПоХсТ РMМьВѓРжТ[ГpГbГPБ[ГWВћНёЧњКJФ≠В∆ВµВƒВҐВйБB3ОЯМ≥ОјСХЦІУxМьПгВ…В®ВҐВƒПdЧvВ∆В»ВйГEГGГnБ[ГМГxГЛГpГbГPБ[ГWМьВѓХХО~НёБAГAГУГeГiМьВѓХХО~НёБAНƒФzРьЧpКіМхНёВћГtГ@ГCГУГsГbГ`СќЙЮЛZПpВрКJФ≠ВЈВйБB

Copyright © ITmedia, Inc. All Rights Reserved.

К÷ШAЛLОЦ

TSMCВЌ2020ФNВ…5nmГvГНГZГXВрЧ ОYБAО©УЃО‘МьВѓГНБ[ГhГ}ГbГvВаО¶ВЈ

TSMCВЌ2020ФNВ…5nmГvГНГZГXВрЧ ОYБAО©УЃО‘МьВѓГНБ[ГhГ}ГbГvВаО¶ВЈ

TSMCВЌ2019ФN6МО28УъБAЙ°ХlОsУаВ≈ЛLО“ЙпМ©ВрКJН√ВµБAУѓО–ФЉУ±СћГtГ@ГEГУГhГКГrГWГlГXВћКTЛµВвГvГНГZГXЛZПpКJФ≠В÷ВћОжВиСg¨»«ВрРа֌µšБBРҐКEН≈СеВћРкЛ∆ГtГ@ГEГУГhГКВ≈В†ВйУѓО–ВћОыЙvВЌКщВ…7nmГvГНГZГXБiN7Бj™ƒВсИшЦрВ∆В»ВЅВƒВ®ВиБA2020ФNВ©Вз5nmГvГНГZГXБiN5БjВрНћЧpµšГ`ГbГvВћЧ ОYКJОnВрЧ\ТиВЈВйБB ФЉУ±СћШIМхЛ@В≈УъМnГББ[ГJБ[»¯ASMLВ…ФsВкВљВћВ©

ФЉУ±СћШIМхЛ@В≈УъМnГББ[ГJБ[»¯ASMLВ…ФsВкВљВћВ©

Ц@Р≠СеКwГCГmГxБ[ГVГЗГУБEГ}ГlГWГБГУГgМ§ЛЖГZГУГ^Б[ВћГVГУГ|ГWГEГАБuКCКOВћГWГГГCГAГУГgВ…КwВ‘ГrГWГlГXБEГGГRГVГXГeГАБvВ≈ВЌБAУъЦ{…®ƒВйУdОqФЉУ±СћОYЛ∆ВћЦҐЧИВрНlВ¶ВйГVГУГ|ГWГEГАБuКCКOВћГWГГГCГAГУГgВ…КwВ‘ГrГWГlГXБEГGГRГVГXГeГАБvВрКJН√БBФЉУ±СћШIМхЛ@Л∆КEВ≈УъМnКйЛ∆В™ГIГЙГУГ_ВћASMLВ…ФsВкВљФwМiВвЧЭЧRВ…В¬ВҐВƒЙрРаµšБB ГiГmГXГPБ[ГЛВћВњВиВћЙeЛњВрЧ}РІБAФЉУ±СћРїСҐСХТuВ™ЦЏОwВЈIoTКИЧp

ГiГmГXГPБ[ГЛВћВњВиВћЙeЛњВрЧ}РІБAФЉУ±СћРїСҐСХТuВ™ЦЏОwВЈIoTКИЧp

БuSEMICON Japan 2016БvВћIoTГCГmГxБ[ГVГЗГУГtГHБ[ГЙГАВ≈УoТdµšУМЛЮГGГМГNГgГНГУОЈНsЦрИхВћРЉК_ОхХFОБВЌБAԊӱўпѥ…®ƒВйБgВњВиБhВћК«ЧЭВ∆БAIoTВрОgВЅВљРґОYРЂМьПгВћОжВиСgВЁВ…В¬ВҐВƒП–ЙоµšБB 72СдВћСХТuВрФЉУъВ≈Й“У≠БAУъЦ{Ф≠БuГ~ГjГ}ГЛГtГ@ГuБvВ™ХѕВ¶ВйКvРVМ^ГВГmВ√В≠Ви

72СдВћСХТuВрФЉУъВ≈Й“У≠БAУъЦ{Ф≠БuГ~ГjГ}ГЛГtГ@ГuБvВ™ХѕВ¶ВйКvРVМ^ГВГmВ√В≠Ви

ОYСНМ§ГRГУГ\Б[ГVГAГА ГtГ@ГuГVГXГeГАМ§ЛЖЙп»«БuSEMICON Japan 2016БvВ≈БAБuГ~ГjГ}ГЛГtГ@ГuВћКJФ≠РђЙ ВрФ≠Х\БBУѓМ§ЛЖЙп»«™РДРiВЈВйГ~ГjГ}ГЛРґОYХыОЃВ…ВжВйРїСҐСХТuБuГ~ГjГ}ГЛГVГКБ[ГYБv72СдВрРЁТuВµБAФЉУ±СћРїСҐНHТцВћВўВ∆ВсВ«ВрГJГoБ[В≈ВЂВйВжВ§В…В»ВЅВљРђЙ ВрГAГsБ[ГЛµšБB ФЉУ±СћВћКJФ≠ЧЌТбЙЇВвГTГvГЙГCГ`ГFБ[ГУНђЧРВ…СќВЈВйНСЙ∆РнЧ™ВрТсМЊБ\Б\JEITA

ФЉУ±СћВћКJФ≠ЧЌТбЙЇВвГTГvГЙГCГ`ГFБ[ГУНђЧРВ…СќВЈВйНСЙ∆РнЧ™ВрТсМЊБ\Б\JEITA

УdОqПоХсЛZПpОYЛ∆Л¶ЙпБiJEITAБjВћФЉУ±СћХФЙпВЌ2021ФN5МО19УъБAМoНѕОYЛ∆П»В…СќВµБuНСНџЛ£СИЧЌЛ≠ЙїВрОјМїВЈВйВљВяВћФЉУ±СћРнЧ™БvВ∆µšТсМЊПСВрТсПoµš±В∆ВрФ≠Х\µšБB ФЉУ±СћХsСЂВЌ2022ФNИ»Н~В…ПуЛµЙьСPВ©БAО‘НЏВвЦ≥РьЧpУrВ™КgСеВЈВйМ©Т Вµ

ФЉУ±СћХsСЂВЌ2022ФNИ»Н~В…ПуЛµЙьСPВ©БAО‘НЏВвЦ≥РьЧpУrВ™КgСеВЈВйМ©Т Вµ

ГKБ[ГgГiБ[ ГWГГГpГУВЌ2021ФN5МО11УъБA2020ФNВћФЉУ±СћОsПкВћУЃМьВ∆2021ФNИ»Н~ВћОsПкМ©Т ВµВ…К÷ВЈВйРаЦЊЙпВрКJН√µšБBМїНЁБAКeЛ∆КEВ≈Р[НПЙїВЈВйФЉУ±СћХsСЂВћПуЛµВЌ2022ФNИ»Н~В…ЙьСPВ…Мь©§В∆Ч\СzВЈВйБB