TSMCは2020年に5nmプロセスを量産、自動車向けロードマップも示す:組み込み開発ニュース(1/2 ページ)

TSMCは2019年6月28日、横浜市内で記者会見を開催し、同社半導体ファウンドリビジネスの概況やプロセス技術開発への取り組みなどを説明した。世界最大の専業ファウンドリである同社の収益は既に7nmプロセス(N7)がけん引役となっており、2020年から5nmプロセス(N5)を採用したチップの量産開始を予定する。

TSMCは2019年6月28日、横浜市内で記者会見を開催し、同社半導体ファウンドリビジネスの概況やプロセス技術開発への取り組みなどを説明した。世界最大の専業ファウンドリである同社の収益は既に7nmプロセス(N7)がけん引役となっており、2020年から5nmプロセス(N5)を採用したチップの量産開始を予定する。日本市場ではスマートフォンおよび自動車領域で成長を狙う。

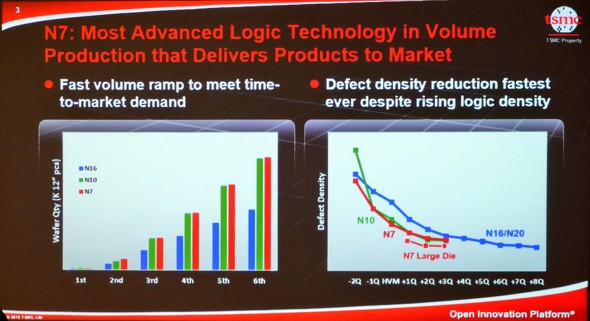

記者会見では、5nmプロセスの第2世代(N5P)までの各プロセスルールについて概要が示された。TSMCでビジネスディベロップメント担当バイスプレジデントを務めるケビン・ジャン氏は、同社の量産最先端プロセスであるN7について「全宇宙で見ても最も高度なテクノロジー」だと述べる。

その理由として、トランジスタの微細化による性能向上の他にウエハー生産量がこれまでのプロセスと比較して急拡大できていること、欠陥密度の減少がこれまで以上に速いペースで進んでいることを挙げる。

次世代プロセスの「N7+」から「N5P」まで順当に性能向上

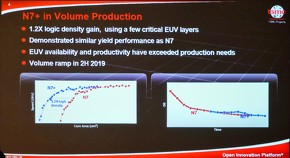

N7の次世代量産プロセスとなる「N7+」では、現世代のN7と比較して20%のトランジスタ密度向上を実現する。N7+ではいくつかのメタル層にEUV(極端紫外線)リソグラフィが導入されており、歩留まりはN7とほぼ同程度にまで至ったとする。2019年下半期から量産開始される予定だ。

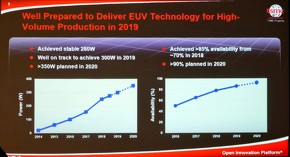

半導体業界はEUVの実用化で多くの困難に直面した。その1つがウエハー処理のスループットに直結するEUV光源の高出力化である。業界では、EUVの量産適応には最低でも250Wの光源が必要との見方が多数を占めていたが、2012年頃まで光源出力は約20W程度だった。2016年より光源出力増加の勢いが加速し、半導体露光装置で世界トップシェアのASML(オランダ)は2017年7月に250W光源を用いたデモを発表するまでに至った。TSMCでは現在安定した光源出力として280Wを達成しており、2019年中に300W実現への道筋をつけた。また、2020年には光源出力350W以上を目指す。

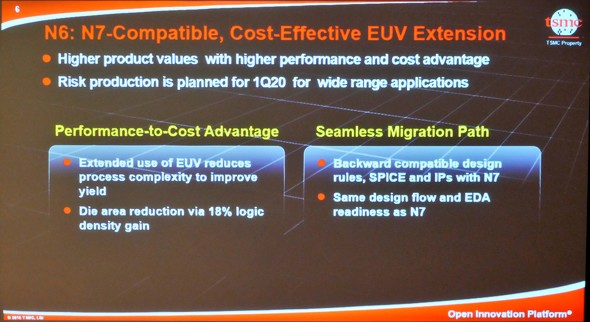

N7+に続くプロセスは、マイナーアップデートの位置付けとなる「N6」と、メジャーアップデートとして大きく性能が向上する「N5」に分かれる見込みだ。N6は2020年第1四半期から量産に向けた準備段階であるリスク生産が始まる。N7から設計面の互換性を維持しつつもEUVの適応メタル層を増やし、N7比で18%の微細化を行った。

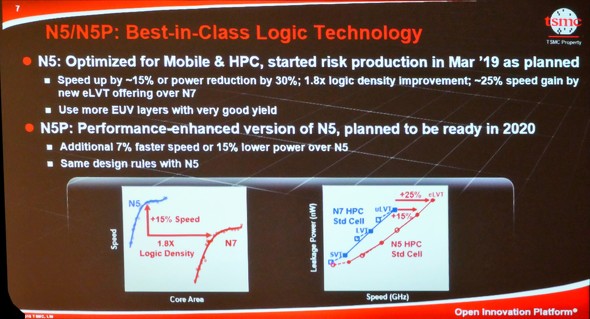

N5は現在リスク生産中で、モバイルとHPC(High Performance Computing)用途に最適化して設計された。N7比で80%の微細化と、15%の高速化もしくは30%の消費電力低減が見込めるとする。さらに、eLVT(extremely Low Voltage Threshold)トランジスタを採用することで、N7比25%の高速化を実現するという。

N5の性能強化バージョンとして「N5P」も用意されており、N5比で7%の高速化もしくは15%の消費電力低減が可能だ。N5と同一の設計ルールを適応し、2020年のリスク生産開始が予定されている。

Copyright © ITmedia, Inc. All Rights Reserved.