TOPPERSが64ビットRISC-Vに対応、リアルタイムOSカーネルを公開:組み込み開発ニュース

TOPPERSプロジェクトは、Sipeedが開発した64ビットRISC-Vプロセッサ搭載ボード「Maixduino」に、μITRON系のリアルタイムOSカーネル「TOPPERS/ASPカーネル(Release 1.9.3)」をポーティングし、オープンソース化する。

TOPPERSプロジェクトは2019年11月20日、Sipeedが開発した64ビットRISC-Vプロセッサ搭載ボード「Maixduino」に、μITRON系のリアルタイムOSカーネル「TOPPERS/ASPカーネル(Release 1.9.3)」のポーティングを実施し、オープンソース化すると発表した。

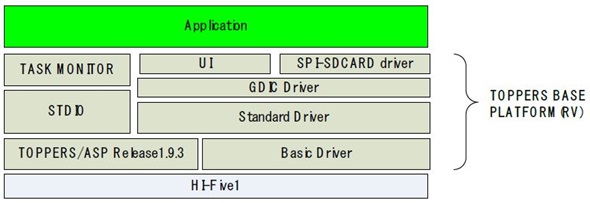

同プロジェクトでは、同年5月にSiFiveが開発した32ビットRISC-Vプロセッサ搭載ボード「HiFive1」に対応したTOPPERS/ASPカーネルを公開。組み込みソフトウェアプラットフォーム「TOPPERS BASE PLATFORM(RV)V0.1.0」を配布している。

今回、ASPカーネルのRISC-V向けプロセッサ依存部を、RISC-V/32とRISC-V/64の両方に対応するよう再設計した。FPU(浮動小数点演算ユニット)処理のプロセッサ依存部に集約したことで、SoCに依存する部分の設定変更だけで、32ビットと64ビットの切り替えやFPUサポート対応の切り替えができる。また、コンパイラには、GNU MCU Eclipseで公開されているGCCコンパイラを採用した。

Maixduinoは、Kendryte製SoC「K210」を搭載。K210は、64ビットRISC-Vプロセッサ「RV64IMAFDC」を2個搭載し、FPUにも対応する。

現在、K210対応のTOPPERS BASE PLATFORM(RV)も開発中だ。デバイスドライバの構成は32ビット版と同じになる。既に、GPIO、DMAC、UART、RTC、SPIのデバイスドライバを「V0.1.1」としてTOPPERSプロジェクトの会員に向けて配布している。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Arm「Custom Instruction」の衝撃、RISC-Vへの徹底抗戦を貫く

Arm「Custom Instruction」の衝撃、RISC-Vへの徹底抗戦を貫く

2019年10月6〜8日にかけてArmが年次イベント「Arm TechCon 2019」を開催した。本連載では、同イベントの発表内容をピックアップする形で同社の最新動向について報告する。まずは、Armのこれまでの方針を大転換することとなった、ユーザーに独自命令を組み込むことを許す「Custom Instruction」について紹介しよう。 TOPPERSがRISC-Vに対応、組み込みソフトウェアプラットフォームを公開

TOPPERSがRISC-Vに対応、組み込みソフトウェアプラットフォームを公開

TOPPERSプロジェクトは、SiFiveが開発したRISC-Vプロセッサ搭載ボード「HiFive1」に対応した組み込みソフトウェアプラットフォーム「TOPPERS BASE PLATFORM(RV)V0.1.0」を発表した。RISC-V用組み込みアプリケーション開発を支援する。 RISC-V上にオープンなセキュリティ基盤を構築する技術研究組合の設立を認可

RISC-V上にオープンなセキュリティ基盤を構築する技術研究組合の設立を認可

エヌエスアイテクス、慶應義塾、産業技術総合研究所、セコム、日立製作所からなるセキュアオープンアーキテクチャ・エッジ基盤技術研究組合は、2019年8月16日付で設立が認可された。 オープンソースのプロセッサIP「SweRV Core」、性能や開発環境が拡充

オープンソースのプロセッサIP「SweRV Core」、性能や開発環境が拡充

Western Digital(ウエスタンデジタル/WD)は2019年6月18日(現地時間)、同社が開発を主導するオープンソースプロセッサIP(Intellectual Property)「SweRV Core」について性能強化や開発環境の拡充などを発表した。 RISC-Vの開発を促進する新しいオープンソースイノベーション

RISC-Vの開発を促進する新しいオープンソースイノベーション

ウエスタンデジタルは、RISC-Vを利用したエコシステムの発展を促進するため、「RISC-V SweRV Core」をはじめとする3つのオープンソースイノベーションを発表した。目的に特化したコンピュータアーキテクチャの開発を促進する。 ヘテロジニアスシステム向けのOS間通信を実現する通信機構

ヘテロジニアスシステム向けのOS間通信を実現する通信機構

TOPPERSプロジェクトは、ヘテロジニアスシステム向けのOS間通信を実現する通信機構「MDCOM」を2016年12月をめどに一般公開する。64ビットARMアーキテクチャに「TOPPERS/FMPカーネル」が対応する。