オープンソースのプロセッサIP「SweRV Core」、性能や開発環境が拡充:組み込み開発ニュース

Western Digital(ウエスタンデジタル/WD)は2019年6月18日(現地時間)、同社が開発を主導するオープンソースプロセッサIP(Intellectual Property)「SweRV Core」について性能強化や開発環境の拡充などを発表した。

Western Digital(ウエスタンデジタル/WD)は2019年6月18日(現地時間)、同社が開発を主導するオープンソースプロセッサIP(Intellectual Property)「SweRV Core」について性能強化や開発環境の拡充などを発表した。同IPのRTL(Register Transfer Level)はGitHubのリポジトリからダウンロードできる。

同プロセッサはISA(命令セットアーキテクチャ)にオープンソースの「RISC-V(リスクファイブ)」を採用する。WDはRISC-Vを活用したプロセッサ開発を進めており、ストレージコントローラーや機械学習など特定用途向けプロセッサへの応用を目指している。

性能向上、デバッグ強化を図ったSweRV Core 1.1

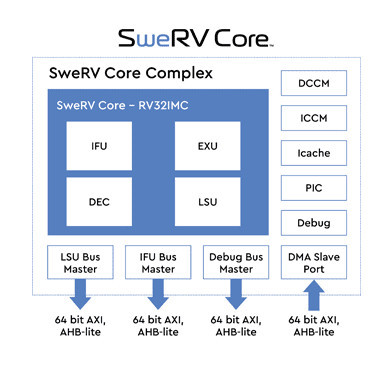

SweRV Coreは9ステージのパイプラインを持つインオーダー実行型スーパースカラプロセッサ。32ビットの「RV32IMC」をサポートし、WDの予測性能では28nmプロセスのCMOSロジック上で最大1.8GHzでの動作を可能としている。組み込み向けベンチマークテストの作成を手掛ける業界団体であるEEMBC(Embedded Microprocessor Benchmark Consortium)が開発するCPUコアベンチマーク「CoreMark」のスコアでは、最大5.0CoreMarks/MHzに達するという。

今回のアップデートでSweRV Coreはバージョン1.1となった。機能強化のポイントは以下の通りとなる。

- RISC-V互換性の向上

- シングルステップのデバッグ時、複数命令が実行されないようにした

- パフォーマンスの改善

- 命令フェッチユニットのメモリアクセス性能を向上

- 除算命令のパフォーマンス改善

- I/Oタイミング制御を改善

- メモリ保護機能(memory protection windows)の追加

- その他

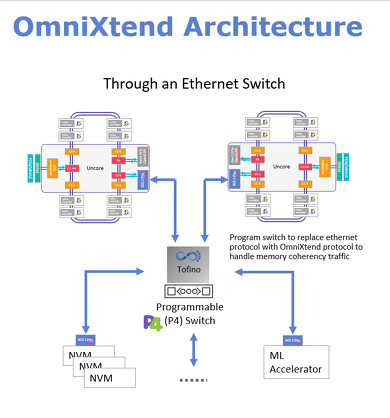

- 誤り訂正の改善

また、WDは同社が開発するオープンネットワークプロトコル「OmniXtend」が、Barefoot NetworkのP4プログラマブルイーサネットスイッチASIC「Tofino」に対応したと発表した。OmniXtendはマルチソケットRISC-Vシステムやヘテロジニアスアーキテクチャシステムでキャッシュコヒーレンシを解決する技術。コヒーレンシメッセージをイーサネットで交換することが特徴だ。

今回の対応により、「CPUやGPU、機械学習アクセラレータ、FPGAといった異なるアーキテクチャ間でも、イーサネットスイッチを介して単一のメモリプールを共有できる」(WD)としている。

SiFiveとの提携でPlatformIO Plusが無償で利用可能に

さらに、WDはRISC-Vチップを手掛けるファブレス半導体メーカーのSiFiveと提携し、IoT(モノのインターネット)デバイスやマイコンの統合開発環境を提供するPlatformIO Labsと戦略的パートナーシップを結んだと発表した。

このパートナーシップ締結により、RISC-Vやその他のアーキテクチャの開発に携わるプログラマーに対して、これまで有償だった「PIO Plus Unified Debugger」や「PIO Uniting Testing Engine」などを無償で提供する。今回の提携により、PlatformIOは「RISC-Vエコシステムなどエンドツーエンドの組み込みテクノロジー設計に向けた完全にオープンソースの支援環境となる」(WD)としている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Western Digital、プロセッサを発表――RISC-Vを活用

Western Digital、プロセッサを発表――RISC-Vを活用

Western Digital(ウエスタンデジタル/WD)は2018年12月4日(現地時間)、オープンソースISA(命令セットアーキテクチャ)である「RISC-V(リスクファイブ)」を採用したプロセッサ「RISC-V SweRV Core」など、RISC-Vに関連する3つのプロジェクトを発表した。 RISC-Vの開発を促進する新しいオープンソースイノベーション

RISC-Vの開発を促進する新しいオープンソースイノベーション

ウエスタンデジタルは、RISC-Vを利用したエコシステムの発展を促進するため、「RISC-V SweRV Core」をはじめとする3つのオープンソースイノベーションを発表した。目的に特化したコンピュータアーキテクチャの開発を促進する。 RISC-V採用のSoC FPGAアーキテクチャ、Linuxにリアルタイム性能を持たせる

RISC-V採用のSoC FPGAアーキテクチャ、Linuxにリアルタイム性能を持たせる

マイクロチップ・テクノロジーは、新たなSoC FPGAアーキテクチャ「PolarFire SoC」を発表した。高機能OSに必要とされる柔軟性やセキュリティ性能、消費電力などの要件を満たし、Linuxにリアルタイム性能を持たせることができる。 RISC-Vのオープンソース開発と導入加速に向けて提携

RISC-Vのオープンソース開発と導入加速に向けて提携

The Linux Foundationは、非営利団体のRISC-V Foundationと提携し、RISC-V命令セットアーキテクチャ「RISC-V」のオープンソース開発と国際的な導入の加速を目指すと発表した。 “プロセッサ”を開発する東芝メモリ、その技術と狙い

“プロセッサ”を開発する東芝メモリ、その技術と狙い

東芝メモリがプロセッサの開発を発表した。現業から離れているように見えるプロセッサの開発を通じて東芝メモリは何を目指すのか。今回発表された技術の概要と開発の狙いを聞いた。 PFNが深層学習プロセッサを開発した理由は「世界の先を行くため」

PFNが深層学習プロセッサを開発した理由は「世界の先を行くため」

Preferred Networks(PFN)は2018年12月12日、ディープラーニングに特化したプロセッサ「MN-Core(エムエヌ・コア)」を発表した。同プロセッサは学習の高速化を目的とし、行列の積和演算に最適化されたものとなる。FP16演算実行時の電力性能は世界最高クラス(同社調べ)の1TFLOPS/Wを達成した。