PFNが深層学習プロセッサを開発した理由は「世界の先を行くため」:人工知能ニュース(1/2 ページ)

Preferred Networks(PFN)は2018年12月12日、ディープラーニングに特化したプロセッサ「MN-Core(エムエヌ・コア)」を発表した。同プロセッサは学習の高速化を目的とし、行列の積和演算に最適化されたものとなる。FP16演算実行時の電力性能は世界最高クラス(同社調べ)の1TFLOPS/Wを達成した。

Preferred Networks(PFN)は2018年12月12日、ディープラーニング(深層学習)に特化したプロセッサ「MN-Core(エムエヌ・コア)」を発表した。同プロセッサは学習の高速化を目的とし、行列の積和演算に最適化されたものとなる。

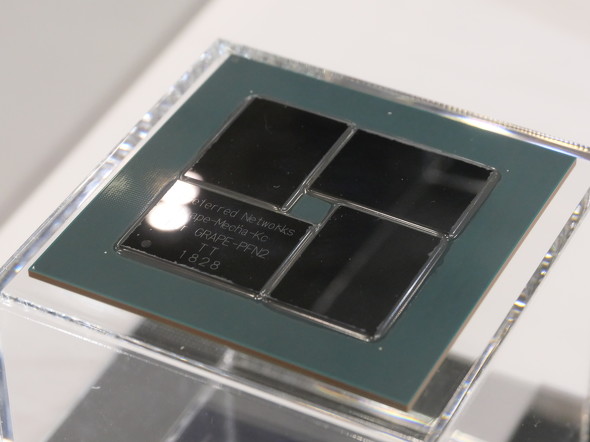

同チップの製造を担当するファウンドリはTSMCで、12nmプロセスによって開発された。ピーク性能はFP64(倍精度)で32.8TFLOPS、FP32(単精度)で131TFLOPS、FP16で524TFLOPSとなる。消費電力の予測値は500Wだ。FP16(半精度浮動小数点)演算実行時の電力性能は世界最高クラス(同社調べ)の1TFLOPS/Wを達成し、「GPUと比較して電力効率は2倍」(同社担当者)であることが特徴だ。

同チップでは、ディープラーニングの学習処理で利用頻度が低い条件分岐といった複雑な命令を排しつつ、CNN(畳み込みニューラルネットワーク)の畳み込み演算などで頻発するSIMD命令の処理に力点を置いたシンプルなマイクロアーキテクチャを採用。大量のデータを一度に処理することを目指した。

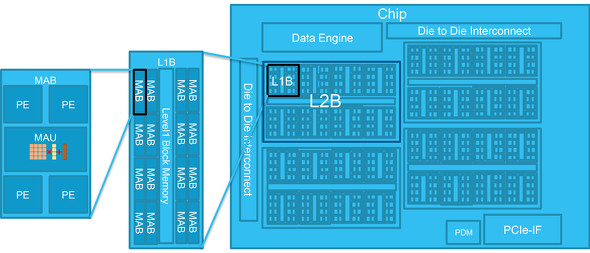

1パッケージは4個のダイで構成し、ダイ間インターコネクトで相互に接続される。1個のダイには512個の行列演算器ブロック(MAB:Matrix Arithmetic Block)が集積されており、行列演算器ブロックは1個の行列演算器(MAU:Matrix Arithmetic Unit)と4個のプロセッサエレメントが含まれる。プロセッサエレメントは整数演算器を持ち、ディープラーニングで頻繁に使用する命令をハードウェアで実装した。

このように階層的なプロセッサ構造としたことで、分配、結合、放送、縮約といった複数モードで階層間のデータ移動が可能となった。これにより柔軟なプログラミングに対応するという。

「世界の先を行く研究には、世界の先を行く計算資源が必要」

PFNは「SEMICON Japan 2018」(2018年12月12〜14日、東京ビッグサイト)に出展し、MN-CoreとMN-Coreを搭載したPCI Express ボード「MN-Core Board」、MN-Core Boardを搭載するラックマウントサーバ「MN-Core Server」を参考展示した。

MN-Coreを開発した経緯について、同社担当者は「社内からさらに高速な計算システムを求める声が多く上がってきたこと、また西川(同社社長の西川徹氏)が以前よりプロセッサを開発したいという思いがあり、プロセッサの開発を進めることとなった」と語る。同社はMN-Coreの論理設計と検証、MN-Core Boardの回路設計を社内で進め、他の工程はパートナーの協力を得たとする。

また、MN-Coreや同チップを活用するハードウェアについて、外販や他社への計算資源提供は「現時点では考えていない」(同社担当者)とし、「全て社内の研究リソースとして展開し、当社のディープラーニング用フレームワーク『Chainer』の開発に生かす」方針だ。

「他の12nmロジックチップと同じくらいの予算感で開発した」とする同チップの開発費用は数十億円以上と見込まれる。この開発費用の回収について、同社担当者は「われわれが世界最先端の研究のさらに先を行くためには、計算能力も世界最先端の先を行かなければ達成できない。リサーチャーが求める計算能力をGPUよりも高い電力効率を持つMN-Coreが提供することで、彼らが世界最先端の先を行く研究成果を生み出すことができる。それが投資のリターンになる」と語る。

一方で、「MN-Coreは行列の積和演算に特化しているため、特殊な数学関数が入るニューラルネットワークの学習は苦手」とし、MN-CoreはGPUを完全に置き換えるものではないとする。同社ではこれらを組み合わせて活用することを検討中だ。

Copyright © ITmedia, Inc. All Rights Reserved.