ダメ半導体ベンチャーだったLattice SemiconductorのV字復活劇はPLDとともに:プログラマブルロジック本紀(9)(3/3 ページ)

FPGAに代表されるプログラマブルロジックICの歴史をたどる本連載。第9回は、AlteraやXilinxと同時期に創業したLattice Semiconductorを取り上げる。当初は会社経営に問題がありチャプター11を申請する状況まで陥った同社だが、新たな経営者を得るとともに、PLDであるGALに事業を絞り込むことでV字復活を遂げる。

pLSI/ispLSIシリーズの発表でさらなる成長へ

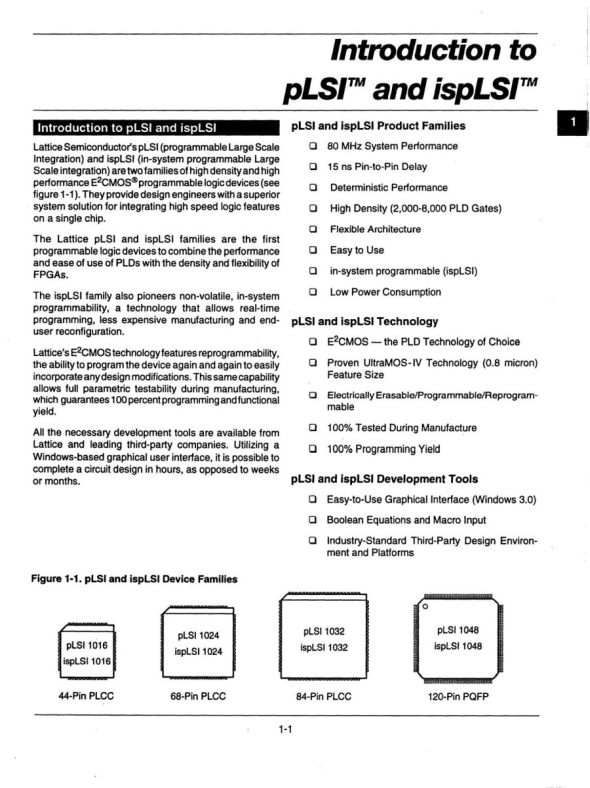

こうして好転した財務基盤に支えられ、1992年3月にpLSI/ispLSI 1000シリーズを合計8製品発表した(図2)。

図2 1992年のpLSI and ispLSI Data Book and Handbookより。1994年にはこの下位モデルである2000シリーズおよび上位モデルである3000シリーズも追加された[クリックで拡大] 出所:Lattice Semiconductor

pLSI/ispLSIシリーズは2000〜8000ゲート相当のPLDで、動作周波数も最大80MHzとなっており、速度はともかく(もうこの当時Fmaxが100MHzのGALが出荷されていた)、ロジック容量が大幅に増加した。図1のMACH 215でも3600ゲート相当だったことを考えれば、この製品の競争力の高さが分かろうというものである。

ここでpLSIとispLSIの違いだが、ベースはpLSIシリーズで、ispLSIシリーズはここにin-system Programing機能を追加したというものだ。GALもそうだが、基本PLDは書き込みに当たって、専用のライターを使ってプログラムを書き込む必要があった(PROMライターと同種のもの)。このため、書き込みにはいったん基板からPLDを抜き、ライターにセットして書き込んだ後で基板に戻すという手間が必要であり、これが理由で量産基板にもPLDにDIP(Dual In-line Package)ソケットが並んでいたわけだ。ただし、図2で分かるように、PLCC(Plastic Leaded Chip Carrier)ならばソケットもまだ現実的だが、PQFP(Plastic Quad Flat Package)はさすがにソケットというわけにもいかない。

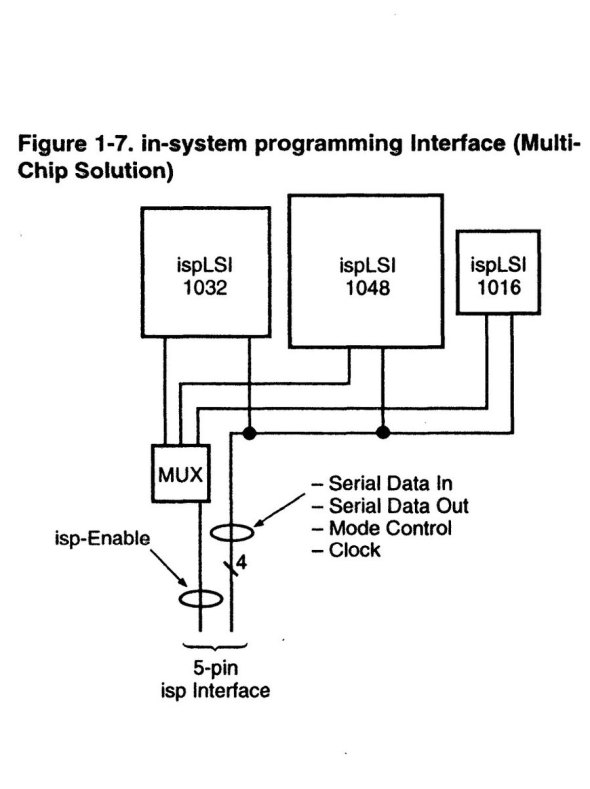

あとソケットを使うと、当然実装面積が増えるしBOMコストも上がる。そこで、PLDを基板に実装した状態で、外部からプログラムを書き換えられるようにしたのがispLSIシリーズというわけだ。ちなみにISPそのものは5線式のシリアル通信であり、複数個のispLSIが実装されている場合にはMUXを挟んだ配線を用意すれば良い。1個だったら、(煩雑に書き換えするのでなければ)配線の先にクリップでも付けてispLSIの足に挟むだけで済むからお手軽である(図3)。

図3 個別にispLSIから配線を引っ張り出すのと、まとめるのとどっちが楽かはケースバイケースだが、個別の方は単にispLSIの横にジャンパピンを立ててつなぐだけだから、それほど苦ではないだろう[クリックで拡大] 出所:Lattice Semiconductor

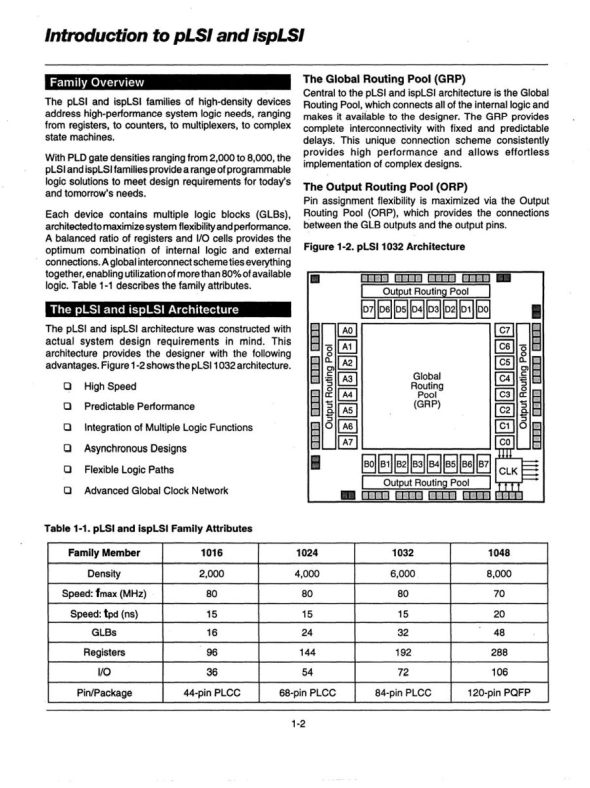

pLSI/ispLSIシリーズの構造自体は、巨大なGALという感じである。全体はGRP(Global Routing Pool)とORP(Output Routing Pool)、GLB(Global Logic Block)から構成される(図4)。

図4 中央がGRPで、その周囲に8つづずつ並ぶA0〜A7/B0〜B7/C0〜C7/D0〜D7がGLP、GLPの外側にORPが配される格好[クリックで拡大] 出所:Lattice Semiconductor

このGLPは8つずつ並べるルールのようで、pLSI1032は32個(A〜D)だが、p1016は16個(A〜B)、p1024は24個(A〜C)、pLSI1048は48個(A〜F)となっている。個々のGLBの内部は図5のような感じであり、これが16〜48個並んでいるわけだ。

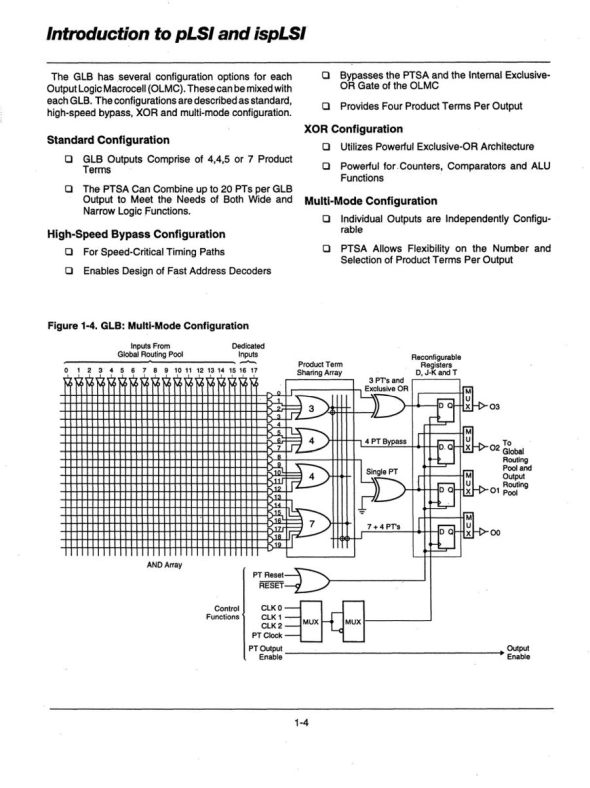

図5 まずLogic Array(AND Array)があり、次にProduct Term Sharing Arrayが入って、最後に4出力のOLMC(Output Logic Macro Cell)が配され、GRPないしORPに接続される形となる。Logic Arrayの入力は当然GRPから[クリックで拡大] 出所:Lattice Semiconductor

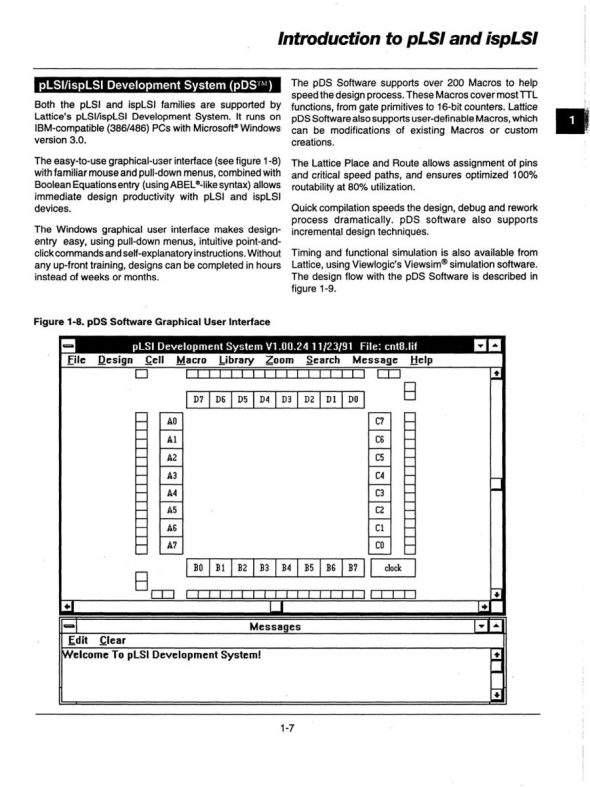

言ってみれば、大容量のGALを16〜48個内蔵し、さらにお互いが相互接続できる仕組みになっている。これは既存のPAL/GALを使い慣れたユーザーにはプログラミングが容易な構造だ。LatticeはこのpLSI/ispLSIの発表に合わせ、pDS(pLSI/ispLSI Development System)というWindows上で動作する開発ツールも提供しており(図6)、好評を博した。

図6 Windows 3.0がちょっと古めかしい感は否めないが、プログラミングはABEL風(DATA-I/Oという会社が提供したABLEという論理記述ツールがこの頃非常に広く使われていた)ということで、エンジニアも取っつきやすかったものと思われる[クリックで拡大] 出所:Lattice Semiconductor

それもあってか同社の株価は1992年に入って70%も上昇した。(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- 連載「プログラマブルロジック本紀」バックナンバー

Xilinxの訴訟や3度のIPO延期を耐えたActelは晴れてFPGAベンダーの3位グループに

Xilinxの訴訟や3度のIPO延期を耐えたActelは晴れてFPGAベンダーの3位グループに

FPGAに代表されるプログラマブルロジックICの歴史をたどる本連載。第8回は、第7回に引き続きActelを取り上げる。Antifuseの課題やXilinxの訴訟、3度のIPO延期を耐えたActelはFPGAベンダーの3位グループに加わることになる。 独創的なロジック記憶手法で違いを見せつけたActelはいかにして誕生したのか

独創的なロジック記憶手法で違いを見せつけたActelはいかにして誕生したのか

FPGAに代表されるプログラマブルロジックICの歴史をたどる本連載。第7回は、Altera/Xilinxに次ぐFPGAベンダーとして知られるActelについて紹介する。Antifuseという独創的なロジック記憶手法により、PALやPLD/CPLDと比べてゲート密度を高めることに成功したものの、半導体製造委託では苦心することになる。 飛躍するXilinx、AMDとの因縁も既に始まっていた!?

飛躍するXilinx、AMDとの因縁も既に始まっていた!?

FPGAに代表されるプログラマブルロジックICの歴史をたどる本連載。第6回は、第5回に続きXilinxの話になる。創業時の業績はイマイチだった同社だが、1989年度に黒字化を果たし飛躍していく。また、最終的にXilinxを買収したAMDとの因縁が既に始まっていた。 FPGAを発明したXilinxとセイコーエプソンの知られざる深イイ関係

FPGAを発明したXilinxとセイコーエプソンの知られざる深イイ関係

FPGAに代表されるプログラマブルロジックICの歴史をたどる本連載。第5回は、Alteraの成長をけん引したCPLDの製品展開などについて取り上げた第4回から少し時間を巻き戻して、Alteraの競合であるXilinxの創業前後の時期について触れてみたい。 レナード・ニモイがAlteraのCPLDを隆盛に導いた!? Xilinxとの競合も始まる

レナード・ニモイがAlteraのCPLDを隆盛に導いた!? Xilinxとの競合も始まる

FPGAに代表されるプログラマブルロジックICの歴史をたどる本連載。第4回は、隆盛を極めたAlteraのCPLDの事業や製品の展開について取り上げる。また、この時期からAlteraとXilinxの競合も始まった。