Alteraの創業によるCPLDの萌芽でプログラマブルロジックはさらなる進化へ:プログラマブルロジック本紀(3)(3/3 ページ)

FPGAに代表されるプログラマブルロジックICの歴史をたどる本連載。第3回は、現在のプログラマブルロジック市場でもさまざまな意味で存在感を放っているAltera(アルテラ)の創業と、CPLDの萌芽となる同社のEP300を取り上げる。

マクロセルの複数搭載で出力段のラインアップをカバー

さて、このEP300は、20ピンのPALの置き換えを狙った製品となった。PALの場合、前回紹介した通り出力段のラインアップが複数種類用意され、目的にあったものを選んで使うことになっていた。逆に言えば、常時複数種類のPALを用意して使い分けなければならないことを意味する。

これに対してEP300は、まずMacrocell(マクロセル)と呼ばれるものを構築した(図1)。

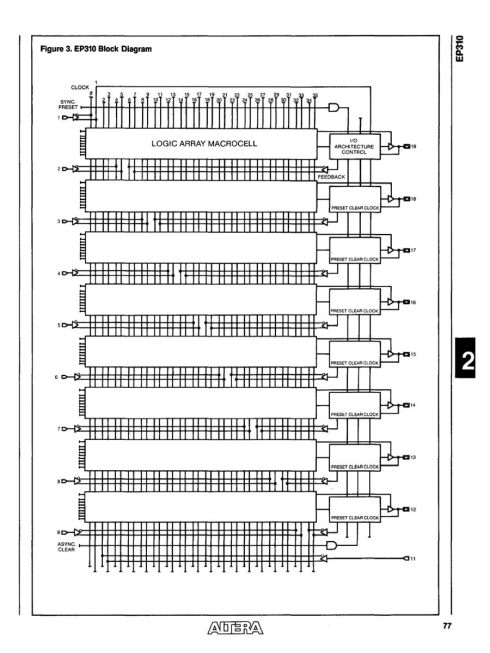

図1 EP310のMacrocellのデータシート(いろいろと探したがEP300のデータシートは見つからなかったので代わりに)。構造そのものはEP300とほぼ変わらない。1〜9+11番ピンがInput(1はClockと共用)、12〜19番ピンがInput/Outputとなっている[クリックで拡大] 出所:Altera Data Book

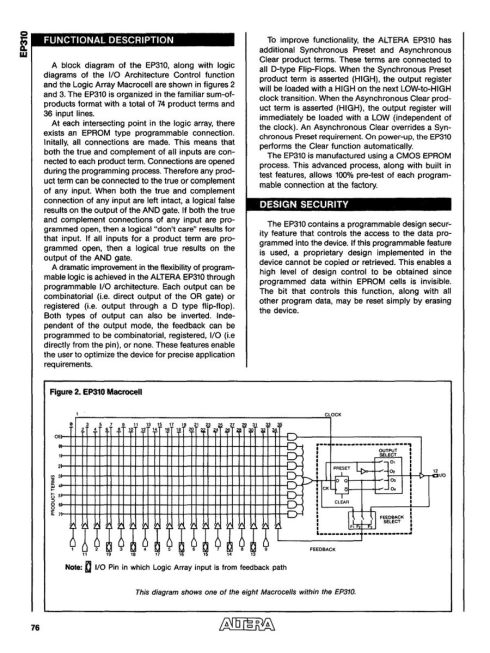

そして、このMacrocellを8つ搭載したものがEP300という構造になっている(図2)。

こうした構造を取ることで、PALの全ての出力段のラインアップをおおむねカバーできていた上に、PALでは不可能な組み合わせも構築できていた(“We did a superset of I suppose all the 20-pin PAL devices that would have been covered by MMI”)としている。つまり、さまざまな種類のPALを全てEP300で代替することを狙い、それが成功したというわけだ。

このようにPALの代替品としては素晴らしいように思えるEP300だったが、大きな欠点は速度であった。EP300の場合、入力から出力までのレイテンシは90ns程度、要するに10M〜11MHz動作でしかなかった。データシートには13.3MHzとか記載されていたらしいが、これは数字を盛ったものであり、実際には11MHzにやや届かないというのが精いっぱいだった。MMIのPALのレイテンシは、定格25ns/最大45nsであり、定格で比較するとEP300の4倍弱高速であり、この点はどうにもならなかった。ちなみに図1と図2で示したEP310は、EP300の高速版でありレイテンシはEP310が最大50ns、EP310-3が最大40ns、EP310-2が最大35nsとなっている。EP310-2だとかなりMMIのPALに近い速度になっているが、完全に追い付くには至っていない。

それでも世の中の顧客の全てがPALのような速度を必要としているわけではなく、そうした顧客にとってはEP300の柔軟性の高さがむしろセールスポイントとして大きく評価されることになる。EP300は1984年に発表されるがこれは大ヒットし、1985年にAlteraは早くも黒字化を達成する。

ちなみにこの時期のAlteraというかEP300の競合となったのはLattice Semiconductorだった。同社もAltera同様1983年に創業したが、CMOSを利用したGALを開発して販売したという話は前回の後半で説明した通りである。Alteraとの違いは、紫外線で消去するUV CMOSのEPROMの代わりに、電気的に消去可能なE2(Electrically Erasable)EPROMのCMOSを利用して構築したことと高速性が売りだった。

LatticeのGALはレイテンシが15nsとMMIのPALよりも高速であり、当時Latticeはこの高速性と紫外線を使う必要が無い点を大きなアピールポイントとし、やはり業界で急速にシェアを伸ばしていった。同様にAMDもPALの欠点だった信頼性の低さ(例えばMMIのPALはチタンタングステンヒューズを利用しており、これが理由で不良率が結構高かった。AMDはここに信頼性の高い白金シリサイドヒューズを採用して不良率を劇的に下げた)を改善したり、22ピンの22V10という「やや大きい」PALを開発したり、という形でシェアを伸ばしていく(この22V10はLatticeもすぐに追従した)。

こうした形で競合メーカーが複数あっても、互いが食い合わずに成長できたのは、プログラマブルロジック市場が急成長していたからだと思われる。そして急成長する市場には、Alteraが次の手を打つのに十分な余地があった。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- 連載「プログラマブルロジック本紀」バックナンバー

プログラマブルロジック市場を創り出した「PAL」は逆転のひらめきから生まれた

プログラマブルロジック市場を創り出した「PAL」は逆転のひらめきから生まれた

FPGAに代表されるプログラマブルロジックICの歴史をたどる本連載。第2回は、プログラマブルロジック市場が創り出したPAL」と、PALの欠点を改良したGALについて紹介する。 プログラマブルロジックの誕生――CPLD前史

プログラマブルロジックの誕生――CPLD前史

FPGAに代表されるプログラマブルロジックICの歴史をたどる本連載。第1回は、プログラマブルロジックが誕生した1970年代の状況や、PLDのご先祖様となるPLAについて紹介する。【訂正あり】 いま振り返るFPGA普及・発展の歴史 〜日本上陸からおよそ20年〜

いま振り返るFPGA普及・発展の歴史 〜日本上陸からおよそ20年〜

FPGAに関するさまざまなテーマをお届けする本連載。記念すべき第1回はFPGAの概要と各年代のエポックメイキング、そして最新動向を紹介する ASICとFPGAの対比で見る“転換点”

ASICとFPGAの対比で見る“転換点”

ASICとFPGAが迎えた本格的な転換点とは? 双方の特長を踏まえたうえで、半導体製造プロセスにおけるテクノロジ・ギャップについて解説する いまさら聞けない FPGA入門

いまさら聞けない FPGA入門

あなたは、人に「FPGA」を正しく説明できるだろうか? いまや常識となりつつあるFPGAについて、あらためてその概念から仕組み、最新動向までを解説する。(編集部)