プログラマブルロジック市場を創り出した「PAL」は逆転のひらめきから生まれた:プログラマブルロジック本紀(2)(1/3 ページ)

FPGAに代表されるプログラマブルロジックICの歴史をたどる本連載。第2回は、プログラマブルロジック市場が創り出したPAL」と、PALの欠点を改良したGALについて紹介する。

連載第1回となる前回は「プログラマブルロジックの誕生――CPLD前史」と題して、プログラマブルロジックが誕生した1970年代の状況や、PLDのご先祖様となるPLA(Programmable Logic Array)について紹介した。

PLAはコストとサイズ、伝達遅延に課題

このPLAの次に世の中に出てきたのがPAL(Programmable Array Logic)である。

PALは1978年に、MMI(Monolithic Memories)のJohn Birkner氏によって考案された。1975年9月にMMIに入社したBirkner氏は、MMI唯一のアプリケーションエンジニアとして、当初は同社が販売していたPROM(Programmable ROM)やビットスライス(MMI 6701)を顧客に売り込む仕事をしていたが、上司だったR.Clive Ghest氏(連載第1回で紹介したTTL ICのパイオニアの一人で、ロジックICのAm2504の設計者でもあり、Fairchild→AMD→MMI→AMDと渡り歩いた)に依頼されてPLAの検討を始める。

もともとBirkner氏は前職(Computer Automationでシステム設計を担当。ちなみに同社は1992年に破綻)の際に、PLAのコストとサイズ、そして伝達遅延の問題に気が付いていた。PLAは、PROMに比べればはるかに高速で、相対的に低コストであるものの、それでも通常のTTL ICに比べるとやや大ぶりであり、コストも高く、何より遅延が大きかった。前回も書いたが、82S100もIM5200も、定格で35ns/65nsと結構大きなレイテンシである。これはシステムを高速化する上で大きなボトルネックになりかねないものだった。

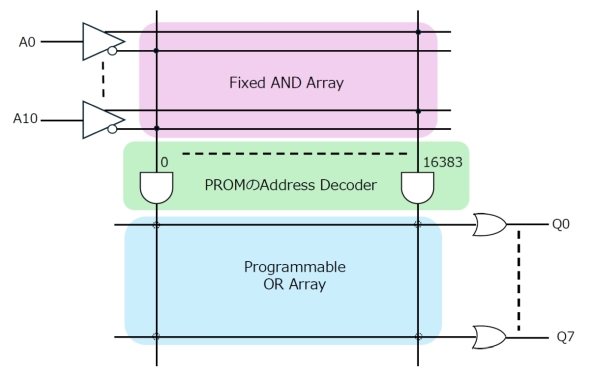

そのPLAを検討中にBirkner氏がひらめいたのが、PLA(というかPROM)のANDとORの役割を逆転させる、という仕組みだった。そもそもPROMの場合、AND Arrayが固定、OR Arrayがプログラマブルという仕組みになっていた(図1)。

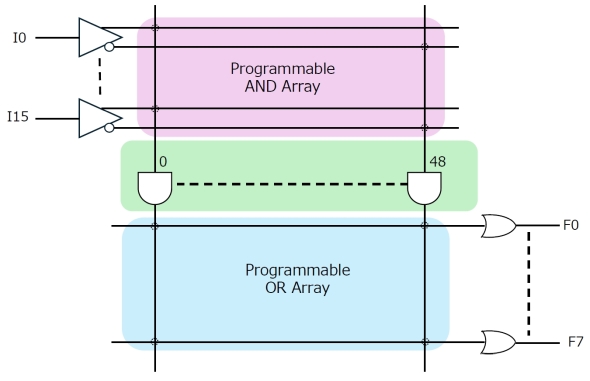

しかし、PROMだからAND Arrayが固定といっても実際にはフルデコードを行っていたわけで、プログラマブルロジックの観点では固定として良いかどうかちょっと微妙なところだ。これの規模を小さくしたのがPLAだが、例えばSigneticsの82S100だと図2のようになる。

AND Arrayのフルデコードを諦め、その代わりにプログラマブルとしたわけだ。この結果として、AND ArrayとOR Arrayの両方にプログラマブルな回路を利用する必要があり、これがPLAの速度が遅い理由であった。

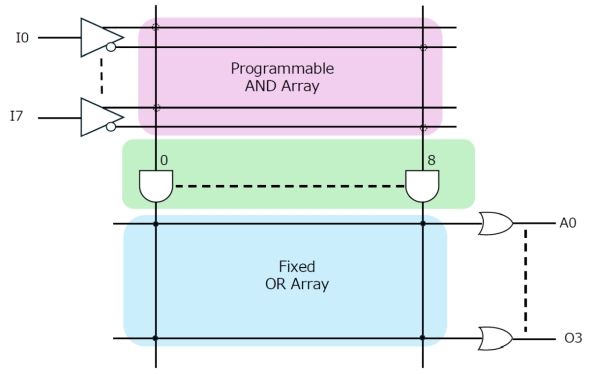

そこでBirkner氏は、AND Arrayの方はプログラマブルとしながらOR Arrayの方を固定にするというアイデアを思い付いた。これだとプログラマブルロジックが半分に減るからそれだけ高速化できる。PLAはまた、そもそも回路規模が大きかった。14ないし16入力、8出力という構成だったが、これだと回路的に持て余す場合もあった。そこでもっと回路規模の小さなものも用意することにした。こうして、コストを下げつつレイテンシも短くすることに成功したのである(図3)。

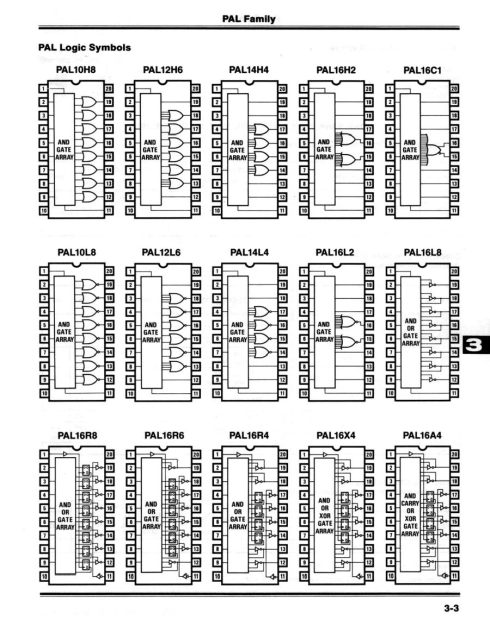

ここでOR Arrayを固定化してしまうと、今度は出力に自由度が減るという問題が生じることになるが、PALではこれに対してさまざまな出力を用意するという形で対応した(図4)。

Copyright © ITmedia, Inc. All Rights Reserved.