新リソグラフィ技術「DLT」を3Dパッケージ基板へ、AMATとウシオ電機が協業:FAニュース

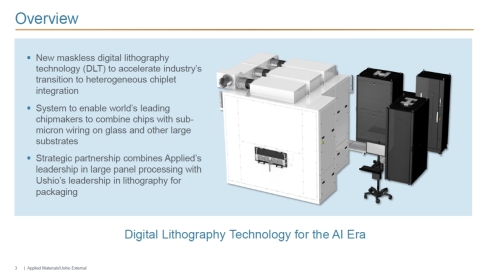

アプライド マテリアルズ(AMAT)とウシオ電機が、3Dパッケージ基板向けのリソグラフィ技術「DLT(Digital Lithography Technology)」について説明した。

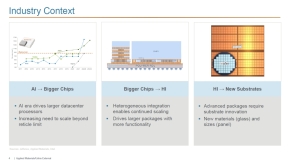

アプライド マテリアルズ(Applied Materials、以下AMAT)とウシオ電機は2023年12月15日、東京都内で会見を開き、同月12日に戦略的パートナーシップの締結を発表した3Dパッケージ基板向けのリソグラフィ技術「DLT(Digital Lithography Technology)」について説明した。生成AI(人工知能)を中心とするHPC(高性能コンピューティング)向け半導体市場の拡大によって3Dパッケージ基板の大型化と微細化が求められており、DLTの基盤技術を持つAMATと、3Dパッケージ基板を含めたプリント基板向けリソグラフィ装置大手のウシオ電機が協業することでいち早く市場のニーズに応えていく構えだ。

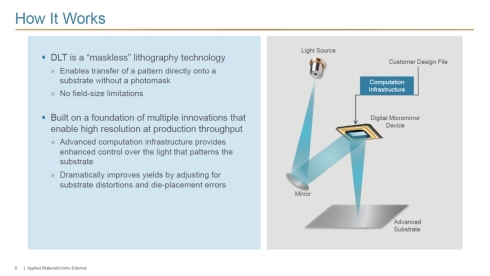

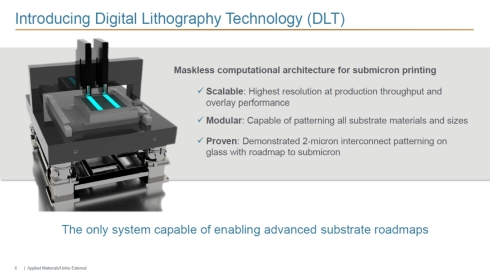

DLTは、紫外光レーザーを用いてプリント基板の回路パターンを直接描画(直描)するリソグラフィ技術である。光源から出力されたレーザーをDLP(Digital Light Processing)方式のプロジェクターなどに用いられているMEMSミラーデバイスのDMD(Digital Micromirror Devices)で精密に制御し、プリント基板上に塗布されたフォトレジストを露光することで微細な回路パターンの転写に対応する。このため、回路パターンの原板となるマスクが不要なマスクレスの技術となっている。

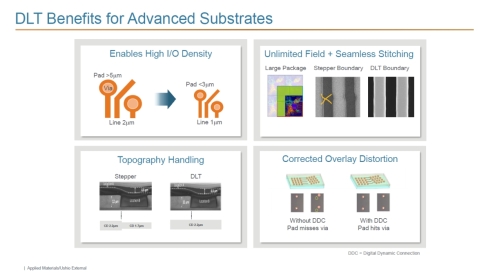

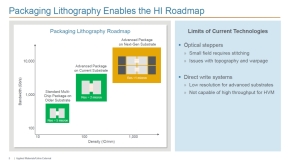

DLTの最大の特徴は、マスクレスで回路パターンを直描できる点にある。現行の3Dパッケージ基板の製造では、微細化が求められない基板層は一般的なメタルマスクを用いるプリント基板向けリソグラフィ装置を、微細化が必要な基板層はフォトマスクを用いる半導体向けリソグラフィ装置のステッパーを適用し、使い分けることが多い。このうちステッパーは、一括露光できる面積が小さく、この面積よりも大きいプリント基板を製造する場合には複数回の露光で回路パターンをつなぎ合わせる「スティッチング」を行う必要がある。

ウシオ電機 グループ執行役員兼事業統括本部Photonics Solutions GBU長のウィリアム・F・マッケンジー(William F. Mackenzie)氏は「半導体の高性能化と高機能化に対応するために、3Dパッケージ内にはさまざまな半導体チップをより多数積層するHI(Heterogeneous Integration)が求められている。そのためには、微細化に対応するとともにより面積の大きな3Dパッケージ基板が必要だ。マスクレスで回路パターンを直描できるDLTはこのニーズを満たす唯一の技術だ」と語る。

その一方で、マスクレスの直描技術の課題としては、処理速度(スループット)と位置合わせ精度の両立が挙げられる。ウシオ電機は、レーザー直描タイプ(Laser Direct Imaging、LDI)のプリント基板向けリソグラフィ装置を長年手掛けており累計で4000台以上を販売しているが、処理速度と位置合わせ精度の両立に課題があった。AMAT グループバイスプレジデント兼セミコンダクタ プロダクトグループ ジェネラルマネージャーのスンダー・ラマムルティ(Sundar Ramamurthy)氏は「DLTは、独自のコンピュータ処理を組み込むことで処理速度と位置合わせ精度の両立を実現した。3Dパッケージ基板に用いられる有機基板やガラス基板はシリコンウエハーと比べると平たんではないため対応は困難だが、DLTであればこの問題も解決できる」と説明する。

DLTは、既に線幅2μmの回路パターン転写の製造実証が行われており、複数の顧客向けに量産装置も出荷している状況にある。また、DLTの技術ポテンシャルとしては、線幅で1μm以下のサブミクロン、パッド部の直径で3μm以下にも対応可能だとしている。

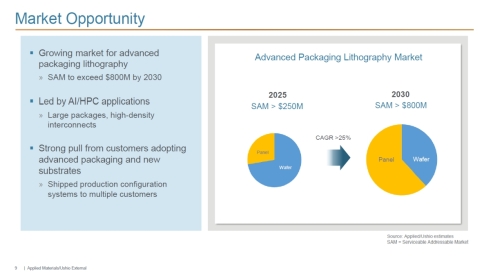

AMATとウシオ電機の調査によれば、3Dパッケージを含めた先進半導体パッケージ向けリソグラフィ装置の市場規模は、2025年の2億5000万米ドルから2030年には3倍以上の8億米ドル(約1130億円)に拡大する。同市場は、2025年時点では現行の3Dパッケージで広く用いられているインターポーザーの基板であるシリコンウエハー向けが70%以上を占めているが、2030年にはDLTがけん引役となって有機材料やガラスを用いるプリント基板向けが60%以上を占めるようになる見込みだ。

なお、両社の協業は、AMATがDLTの技術とディスプレイ向けで30年間培ってきた大型基板向けのノウハウを融合して研究開発を担当し、プリント基板向けリソグラフィ装置を長年展開してきたウシオ電機がDLTを組み込んだ装置の開発やその販売を担当することを基本としているが「今後の事業進捗によっては互いの役割が広がっていく可能性もあり、役割分担にはこだわらない」(マッケンジー氏)としている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

TSMCとイビデンが3次元実装で連携強化、先端パッケージ基板の生産性を10倍に

TSMCとイビデンが3次元実装で連携強化、先端パッケージ基板の生産性を10倍に

TSMCは同社が主導する半導体製造のオープンイノベーションの枠組みであるOIPエコシステムや、3次元実装に向けたアライアンス「TSMC 3DFabric Alliance」、3次元実装プロセスにおいてツールや材料の相互利用を可能にする標準規格「3Dblox」について説明した。 TSMCはなぜ台湾外初となる3DICのR&D拠点をつくばに設立したのか

TSMCはなぜ台湾外初となる3DICのR&D拠点をつくばに設立したのか

台湾の半導体受託製造大手であるTSMCは2022年6月24日、茨城県つくば市の産業技術総合研究所つくばセンター内に設置した「TSMCジャパン3DIC研究開発センター」の開所式を行った。同センターでは半導体微細化の限界が予想される中、後工程の3次元パッケージ技術の量産を可能とするための技術開発を日本の材料メーカーや装置メーカー、研究機関との共同研究で実施する。 チップレットなど先端半導体やEV部品を3Dで高速自動検査、オムロンが検査装置拡充

チップレットなど先端半導体やEV部品を3Dで高速自動検査、オムロンが検査装置拡充

オムロンは新たなCT型X線自動検査装置「VT-X950」「VT-X850」を2024年に投入する。半導体検査向けの「VT-X950」は2024年春、EV部品向けの「VT-X850」は2024年2月の発売を予定している。 レゾナックがシリコンバレーに研究開発拠点を開設、AI向け半導体の情報も収集

レゾナックがシリコンバレーに研究開発拠点を開設、AI向け半導体の情報も収集

レゾナックは、東京都内で半導体戦略説明会を開き、米国カリフォルニア州のシリコンバレーに半導体のパッケージングおよび材料の研究開発センターであるパッケージングソリューションセンターを開設することを発表した。 オーク製作所が「JOINT2」に参画、次世代半導体パッケージにダイレクト露光を適用

オーク製作所が「JOINT2」に参画、次世代半導体パッケージにダイレクト露光を適用

オーク製作所は、次世代半導体パッケージ技術の評価/検証を行うコンソーシアム「JOINT2」に参画し、開発を進めている次世代ダイレクト露光装置の性能を検証し、顧客提案力を強化する。 昭和電工は第2の創業で「レゾナック」へ、半導体材料事業が成長をけん引

昭和電工は第2の創業で「レゾナック」へ、半導体材料事業が成長をけん引

昭和電工が、昭和電工マテリアルズ(旧日立化成)の統合によって2023年1月1日に発足する新会社「レゾナック」の半導体材料事業について説明。2021年度の統合前2社の業績ベースで、半導体材料事業の売上高は2665億円と世界トップクラスであり、中でも後工程材料については1853億円で圧倒的な世界No.1のポジションにあるという。