ニュース

非パイプライン構造1ステージ化RISC-VプロセッサのFPGAのCPU回路効率を改善:組み込み開発ニュース

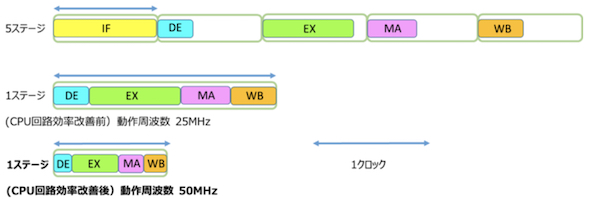

ウーノラボは、RISC-Vを適用した非パイプライン構造の1ステージ化プロセッサについて、FPGAのCPU回路効率を改善した。これにより、動作周波数が従来の検証結果の2倍となる50MHzを記録した。

ウーノラボは2021年4月30日、RISC-V(RV32IM)を適用した非パイプライン構造の1ステージ化プロセッサについて、FPGAのCPU回路効率を改善したと発表した。これにより、動作周波数が従来の検証結果の2倍となる50MHzを記録。同社は、同FPGAのIPコアの販売や特許技術のライセンス供与を開始する。

同プロセッサは、同社の特許技術を用いてIFステージを削除し、1命令サイクルを1ステージ化して1クロックで処理する。分岐や割り込み処理の完了後に次のクロックで元のプログラムに復帰するため、読み込んだプログラムの破棄や再読み込みによる遅延が生じず、低消費電力で効率良く動作する。

回路規模が小さく並列処理にも適しており、IoT(モノのインターネット)機器に組み込める。また、画像処理が必要な自動運転車やAI(人工知能)でのエッジコンピューティングにも使用できる。

同社は今後、アーキテクチャの性能をさらに向上すべく、クロック同期式および非同期式ASICへの実装に取り組む。非同期式ASICは、従来の非同期式回路設計を必要とせず、同期式開発ツールを利用できる点や、輻射ノイズが低減するためサイドチャンネルアタックを抑制できる点がメリットとなる。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Arm「Custom Instruction」の衝撃、RISC-Vへの徹底抗戦を貫く

Arm「Custom Instruction」の衝撃、RISC-Vへの徹底抗戦を貫く

2019年10月6〜8日にかけてArmが年次イベント「Arm TechCon 2019」を開催した。本連載では、同イベントの発表内容をピックアップする形で同社の最新動向について報告する。まずは、Armのこれまでの方針を大転換することとなった、ユーザーに独自命令を組み込むことを許す「Custom Instruction」について紹介しよう。 ルネサスとSiFive、RISC-V技術を活用した次世代車載半導体の共同開発で提携

ルネサスとSiFive、RISC-V技術を活用した次世代車載半導体の共同開発で提携

ルネサス エレクトロニクスとSiFiveは、車載用次世代ハイエンドRISC-Vソリューションの共同開発で提携した。ルネサスはSiFiveからRISC-VコアIPポートフォリオのライセンス供与を受け、次世代車載半導体を開発する。 機能安全規格に対応したRISC-V用開発ツールを提供

機能安全規格に対応したRISC-V用開発ツールを提供

IAR Systemsは、機能安全規格「IEC 61508」および「ISO 26262」認証済みのRISC-V向け開発ツール「機能安全版IAR Embedded Workbench for RISC-V」を提供する。「IAR Embedded Workbench for RISC-V version 1.40.」での適用を予定する。 Cortex-M4とRISC-VにAIアクセラレータを内蔵したマイコン、消費電力は100分の1

Cortex-M4とRISC-VにAIアクセラレータを内蔵したマイコン、消費電力は100分の1

Maxim Integrated Productsは、ニューラルネットワーク向けアクセラレーターを内蔵したマイクロコントローラー「MAX78000」を発表した。低コストで高速のアプリケーション開発を支援する。 ルネサスがRISC-V採用、ArmやRXベースの製品もある産業機器向け32ビット製品で

ルネサスがRISC-V採用、ArmやRXベースの製品もある産業機器向け32ビット製品で

ルネサス エレクトロニクスは、オープンソースのプロセッサコアIPである「RISC-V」を用いた組み込みCPUコアや関連するSoC開発環境のサプライヤーである台湾のアンデスとの技術提携を発表した。ルネサスは新開発のASSPにアンデスのRISC-Vベースの32ビットCPUコアである「AndesCore」を組み込み、2021年下半期にサンプル提供を開始する。 RISC-V向けOSおよび開発ツールの共同研究開発を開始

RISC-V向けOSおよび開発ツールの共同研究開発を開始

イーソル、ユーリカ、京都マイクロコンピュータ、エヌエスアイテクスは、既存のRISC-V開発環境に対し、国内活用の観点から不足しているOSや開発ツールの機能開発と実証評価を開始する。