中国が躍進する半導体国際学会「ISSCC 2020」、採択状況と注目論文を紹介:組み込み開発ニュース(3/3 ページ)

半導体回路に関する国際学会「ISSCC(International Solid-State Circuits Conference)」は2019年11月19日、東京都内で記者会見を開催し、「ISSCC 2020」の概要と注目論文を紹介した。

機械学習領域の注目論文を紹介

記者会見では、ISSCC 2020で発表される注目論文が紹介された。12の技術分科会の内、本稿では機械学習の注目論文を抜粋して紹介する。

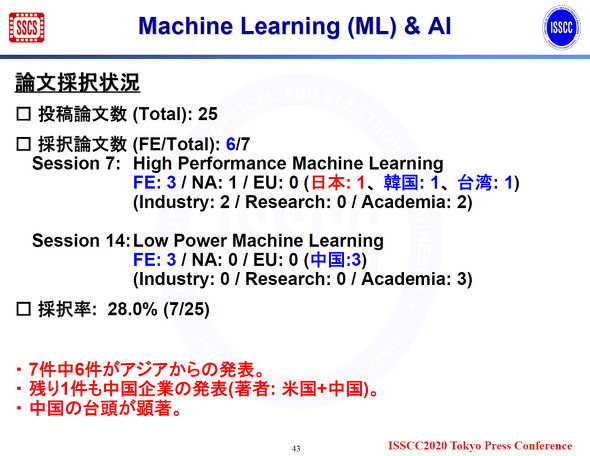

機械学習の技術分科会では、投稿論文数が25件で採択論文数は7件。その内6件がアジアからの発表となるが、残り1件も中国Alibabaに勤める著者が投稿した。よって、同分野はほぼアジア勢が席巻している状況だ。データセンターやモバイル端末での応用に向いた「High Performance Machine Learning」と、極低電力環境での応用を目指す「Low Power Machine Learning」の2セッションに分かれている。

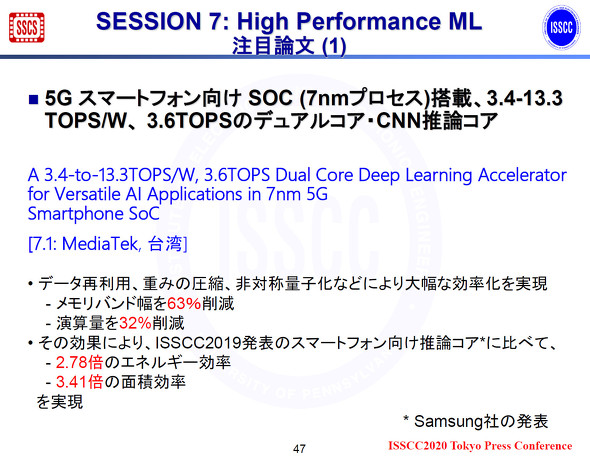

High Performance Machine Learningの注目論文は3件紹介された。MediaTekが発表する「A 3.4 to 13.3TOPS/W, 3.6TOPS Dual Core Deep Learning Accelerator for Versatile AI Applications in 7nm 5G Smartphone SoC」(セッション7.1)では、データ再利用、重みの圧縮、非対称量子化などにより大幅な効率化を実現したことを報告した。Samsung ElectronicsがISSCC 2019で発表したスマートフォン向け推論コアと比較して、2.78倍のエネルギー効率と3.41倍の面積効率を実現したとする。

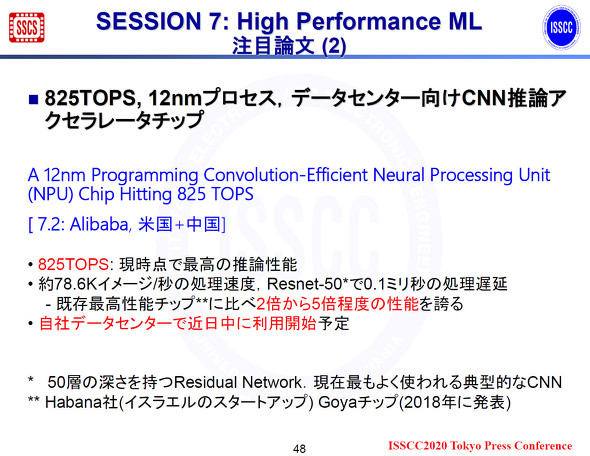

Alibabaが発表する「A 12nm Programming Convolution Efficient Neural Processing Unit(NPU)Chip Hitting 825 TOPS」(セッション7.2)では、現時点で最高の推論性能を持つとされるデータセンター向けCNN(畳み込みニューラルネットワーク)推論アクセラレーターチップを紹介する。1秒あたり約7万8600枚の画像を推論することが可能で、ResNet-50では遅延を0.1ミリ秒まで抑えることができる。既存の最高性能チップ(イスラエルHabana製Goyaチップ)と比較して、2〜5倍程度の性能を発揮するという。

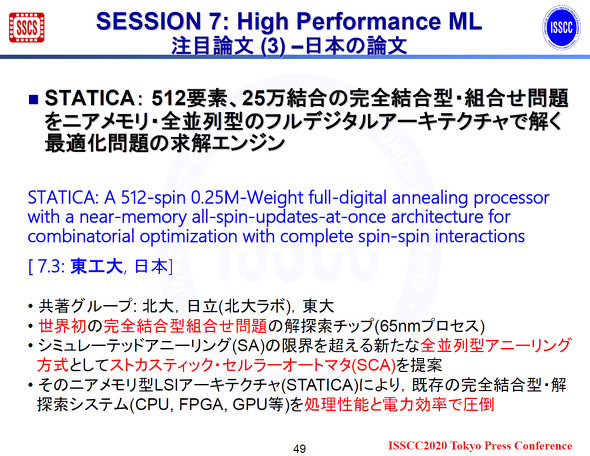

東京工業大学などが発表する「STATICA: A 512 spin 0.25M Weight full digital annealing processor with a near memory all spin updates at once architecture for combinatorial optimization with complete spin spin interactions」(セッション7.3)では、512要素、25万結合の完全結合型組み合わせ問題に向けた世界初の65nmプロセス解探索チップを紹介する。

同論文では、新たに全並列型アニーリング方式としてストカスティックセルラーオートマタ(SCA)を提案。ニアメモリ型LSIアーキテクチャ(STATICA)により、既存の完全結合型解探索システムから処理性能と電力効率で優位に立ったと報告している。

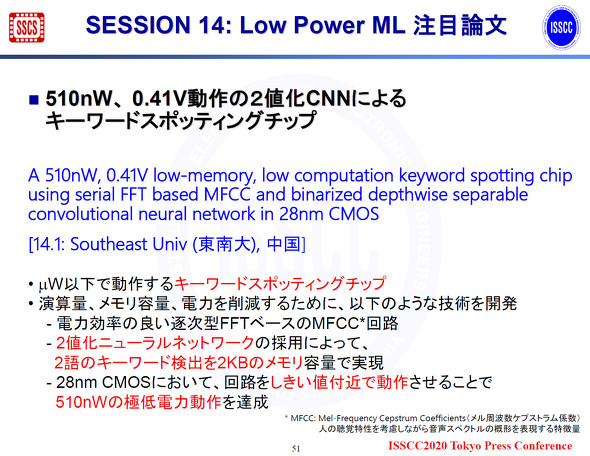

Low Power Machine Learningでは、中国の東南大学が発表する「A 510nW, 0.41V low memory, low computation keyword spotting chip using serial FFT based MFCC and binarized depthwise separable convolutional neural network in 28nm CMOS」(セッション14.1)が注目論文となっている。

同論文では、510nWで動作するキーワードスポッティングチップを報告している。演算量やメモリ容量、電力を削減するため、電力効率の良い逐次型FFTベースのMFCC(Mel-Frequency Cepstrum Coefficients)回路を実装したことや、2値化ニューラルネットワークの採用、28nm CMOS回路をしきい値付近で動作させたとしている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

“プロセッサ”を開発する東芝メモリ、その技術と狙い

“プロセッサ”を開発する東芝メモリ、その技術と狙い

東芝メモリがプロセッサの開発を発表した。現業から離れているように見えるプロセッサの開発を通じて東芝メモリは何を目指すのか。今回発表された技術の概要と開発の狙いを聞いた。 PFNが深層学習プロセッサを開発した理由は「世界の先を行くため」

PFNが深層学習プロセッサを開発した理由は「世界の先を行くため」

Preferred Networks(PFN)は2018年12月12日、ディープラーニングに特化したプロセッサ「MN-Core(エムエヌ・コア)」を発表した。同プロセッサは学習の高速化を目的とし、行列の積和演算に最適化されたものとなる。FP16演算実行時の電力性能は世界最高クラス(同社調べ)の1TFLOPS/Wを達成した。 裏面照射を置き換える? パナソニックが有機薄膜とAPDのCMOSセンサーを発表

裏面照射を置き換える? パナソニックが有機薄膜とAPDのCMOSセンサーを発表

パナソニックは、半導体技術の国際学会「ISSCC2016」で3つのCMOSセンサー技術を発表した。従来のCMOSセンサーに用いられているフォトダイオードを、有機薄膜やアバランシェフォトダイオード(APD)に置き換えることによって感度やダイナミックレンジを向上する技術になる。 仮想化しても車両制御向けのリアルタイム性を確保、ハードウェアで処理時間短縮

仮想化しても車両制御向けのリアルタイム性を確保、ハードウェアで処理時間短縮

ルネサス エレクトロニクスは2019年2月19日、28nmプロセスを採用した次世代車載制御用マイコンに仮想化支援機構を搭載したテストチップを開発し、最大600MHzでの動作を確認したと発表した。自動車メーカーがECU(電子制御ユニット)の機能統合を進めており、1つのマイコンにより多くの機能を搭載することが求められている。テストチップには、これに対応するための技術を搭載した。 デンソーがソニー製イメージセンサーを採用、夜間の歩行者検知が可能に

デンソーがソニー製イメージセンサーを採用、夜間の歩行者検知が可能に

デンソーは、運転支援システムなどに用いられる車載用画像センサーにソニー製イメージセンサーを採用することで、夜間の歩行者認識が可能になったと発表した。 深層学習開発クラウドサービスで、高速かつ安価なGPUが利用可能に

深層学習開発クラウドサービスで、高速かつ安価なGPUが利用可能に

深層学習のプログラムを生成する、ソニーの統合開発環境「Neural Network Console クラウド版」において、産業技術総合研究所が運用する「AI橋渡しクラウド」のGPUが選択可能になった。高速のGUI開発環境を低コストで利用できる。