2nmノードのGAAトランジスタの製造課題を解消する3機種:材料技術(3/3 ページ)

アプライドマテリアルズジャパンは、プレスラウンドテーブル「次世代トランジスタ技術によるAI性能の最大化」を開催し、2nmノードのGAAトランジスタの製造課題を解消する3機種を紹介した。

2nmノードのGAAトランジスタ製造課題を解消する装置

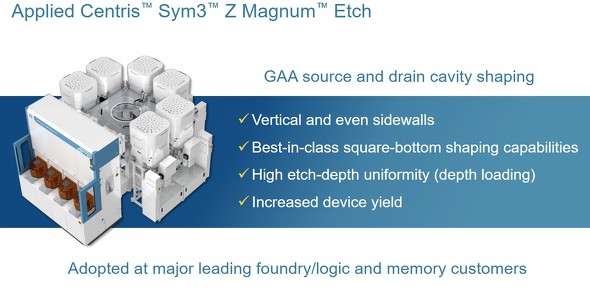

今回のラウンドテーブルの後半では、先端ロジック半導体の省電力化/高性能化に役立つ「GAA(ナノシート)トランジスタ」の製造に向けた最新の装置として、ラジカル処理装置「Viva」、エッチング装置「Sym3 Z Magnum with PVT2」、モリブデン選択成膜装置「Centris Spectral Mo ALD」を紹介した。いずれも、GAA構造のトランジスタの製造に利用される装置だ。

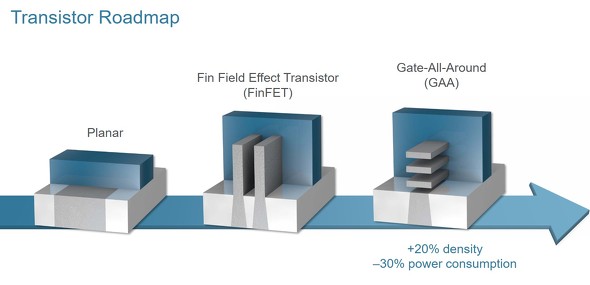

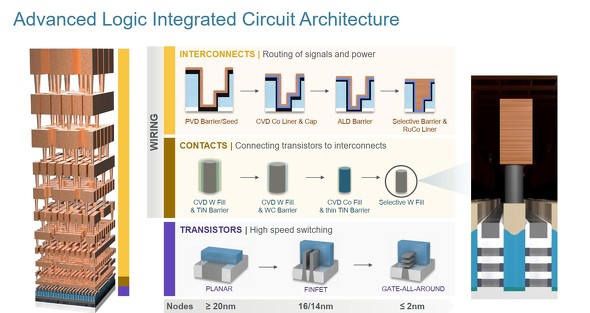

アプライドマテリアルズジャパン 技術本部長 工学博士の松永範昭氏は「まず、主流となったトランジスタはプレーナー型トランジスタ(平面型MOSFET)だ。プレーナー型トランジスタに関しては、さまざまなメーカーがトランジスタ密度を上げるために小型化を進めてきた。しかし、小型化により、リーク電流が大きくなり、ゲートの制御性が低くなるという課題があった。この課題を解消するために、ゲートの制御性を高め、リーク電流を抑えられる立体構造のFinFETが開発され、採用されてきた。現在はさまざまなメーカーで開発された2nmノードのGAAトランジスタが量産に入る段階だ。2nmノードのGAAトランジスタは、FinFETに比べて、トランジスタ密度が20%、パワー効率が30%高いとされている」と述べた。

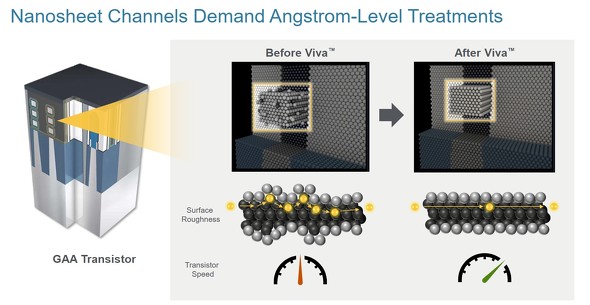

しかし、GAAのチャネル(電子の通り道)となるナノシートの厚みは、わずか5〜10nmだ。この薄さになると、加工後の表面のわずかな凹凸(原子数個分の荒れ)や不純物、結晶欠陥が電子の散乱を招き、トランジスタの動作速度を低下させてしまう。

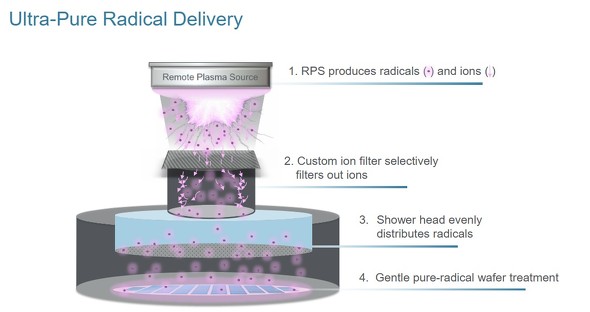

Vivaは、リモートプラズマソース(RPS)と特殊な「イオンフィルター」を組み合わせた装置で、水素ラジカルのみをウエハー表面に作用させることで、原子レベルでの表面平滑化(スムージング)と低欠陥化を実現する。

松永氏は「Vivaは上部のRPSで水素ラジカルとイオンを生じる。イオンは、強い方向性や運動エネルギーを持っており、処理したいチャネルの部分に当たると、何らかの損傷を受ける。そのため、装置の中間部にイオンフィルターを設け、高エネルギーのイオンを99.9%除去できるようにしている。これにより、装置の下部に設置したウエハーに化学的に有効な水素ラジカルを送り、表面のスムージングを行う」と説明した。

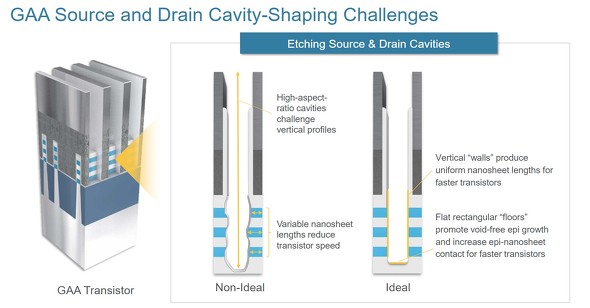

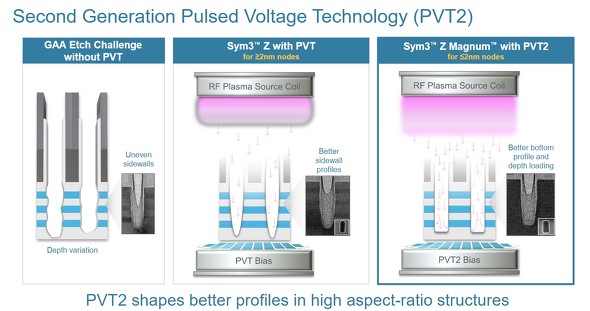

2nmノードのGAAトランジスタでは、ソースドレイン形成において、シリコン(Si)とシリコンゲルマニウム(SiGe)がミルフィーユ状に積層されたナノシートの間に、エピタキシャル成長のための深いトレンチ(溝)を形成する必要がある。材質によってエッチングレートが異なるため、従来技術では側壁が波打ち、後工程での結晶成長に悪影響(ボイドの発生など)があった。

この解決策として、Applied MaterialsはSym3 Z Magnum with PVT2を開発した。Applied MaterialsはSym3 Z Magnum with PVT2は、エッチング装置「Centris Sym3 Z Magnum」と第2世代パルス電圧技術であるPVT2を組み合わせたものだ。同装置は、パルス波を用いてイオンのエネルギーとエッチングの入射角を独立して精密に制御することで、側壁を保護しながら、表面の反応性を上げつつ、削り過ぎることなく深いトレンチを形成できる。高アスペクト比の深いトレンチであっても、フラットな底部と滑らかな側壁を同時に実現する。

「この技術は深いところにきれいなトレンチを掘るという装置で、3D NANDなどのメモリや、最近開発されているDRAMにおける深いトランジスタ加工などにも適用できる」と松永氏はいう。

また、トランジスタと配線をつなぐコンタクトの材料には、長らくタングステンが使用されてきた。タングステンを使用する場合、周囲に「バリアメタル」と呼ばれる高抵抗の膜を張る必要がある。しかし、2nmノードのGAAトランジスタでは、コンタクト全体に占めるバリアメタルの体積割合が増えすぎ、電気抵抗が高いレベルに達してしまうという。

松永氏は「ソースドレインでエピタキシャル層を成長させ、コンタクトを装着し、配線層に信号を送る。この時に重要なのがコンタクトのメタライゼーションだ。メタライゼーションでは、タングステンをコンタクトとしてきれいに成膜するために、バリアメタルあるいはライナーと呼ばれる金属を使わなければならない」と触れた。

この問題を解決する装置として、Applied MaterialsはCentris Spectral Mo ALDを提供している。Centris Spectral Mo ALDは、バリアメタルやライナーを必要としない「モリブデンの選択的(セレクティブ)成膜技術」だ。モリブデンは細く加工しても効率的な電子の流れを維持できるため、オングストロームノードの次世代コンタクト候補として注目を集めている。

この装置は、特定の表面にのみ単結晶モリブデンを直接成長させコンタクトとすることで、微細領域における電子散乱の影響を抑えるとともに、タングステン選択成膜装置「Applied Endura Volta Selective Tungsten」で成膜したタングステンのコンタクトと比べて、コンタクト抵抗を10〜15%以上低減する。

いずれの装置も既に顧客に導入されており、今後は2nmノードのGAAトランジスタの量産に使用される予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「JOINT3」の全貌、パネルレベル有機インターポーザー実現を加速する仕組みとは?

「JOINT3」の全貌、パネルレベル有機インターポーザー実現を加速する仕組みとは?

レゾナックが国内外の27社と連携し、新たな共創プラットフォーム「JOINT3」を設立した。このプラットフォームは、パネルレベル有機インターポーザーという次世代技術の開発を加速させ、半導体産業の未来をどのように変えるのか。 先進的なチップ配線技術を開発、コンピューティングのエネルギー効率向上

先進的なチップ配線技術を開発、コンピューティングのエネルギー効率向上

アプライド マテリアルズは、銅配線を2nmロジックノード以降へ微細化してコンピューティングシステムのエネルギー効率を高める、新たなチップ配線技術を発表した。微細化に加え、新たなLow-k絶縁材料でキャパシタンスの低減と材料強度を両立した。 先端ロジック/メモリチップのパターニングには計測技術のブレークスルーが必要

先端ロジック/メモリチップのパターニングには計測技術のブレークスルーが必要

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回は、半導体の微細化が進展する中で求められている計測技術のブレークスルーについて紹介する。 半導体チップのナノスケール欠陥を分析、AI活用の電子ビーム装置を発表

半導体チップのナノスケール欠陥を分析、AI活用の電子ビーム装置を発表

Applied Materials(アプライド マテリアルズ)は、半導体チップのナノスケールの欠陥を分析できる電子ビーム装置「SEMVision H20」を発表した。数十億ものナノスケール回路パターンに潜在する微細な欠陥を、的確かつ迅速に分析できる。 半導体製造装置業界の特許資産規模ランキング2024を発表

半導体製造装置業界の特許資産規模ランキング2024を発表

パテント・リザルトは、「半導体製造装置業界 特許資産規模ランキング2024」を発表した。1位が東京エレクトロン、2位がApplied Materials、3位がディスコとなっている。