先進的なチップ配線技術を開発、コンピューティングのエネルギー効率向上:研究開発の最前線

アプライド マテリアルズは、銅配線を2nmロジックノード以降へ微細化してコンピューティングシステムのエネルギー効率を高める、新たなチップ配線技術を発表した。微細化に加え、新たなLow-k絶縁材料でキャパシタンスの低減と材料強度を両立した。

アプライド マテリアルズは2024年7月9日、銅配線を2nmロジックノード以降へ微細化してコンピューティングシステムのエネルギー効率を高める、新たなチップ配線技術を発表した。銅配線の微細化に加え、新たなLow-k(低誘電率)絶縁材料により、キャパシタンスの低減と材料強度を両立した。

新たに発表したのは、同社の「Producer Black Diamond PECVD」ファミリーに含まれるLow-k絶縁材料「Black Diamond」の改良版だ。最小誘電率定数(k値)を下げて微細化に対応する他、機械的強度の向上を図った。

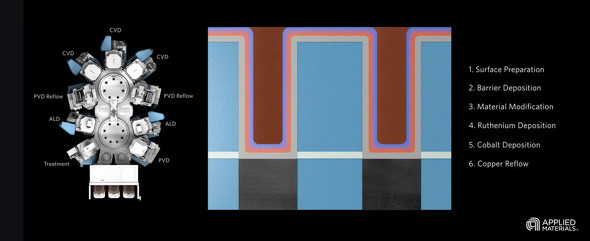

また、最新のインテグレーテッドマテリアルズソリューション(Integrated Materials Solution:IMS)を提供。6つの異なるテクノロジーを1台の高真空システムに統合しており、その1つが、銅配線を2nm以降へ微細化する技術だ。

ルテニウムとコバルトを組み合わせた二元金属(RuCo)を使用し、ライナー厚を33%低減して2nmにしている。さらに、表面特性を改善してボイドフリーの銅リフローを可能にし、電線抵抗を最大25%に低減。チップのパフォーマンスと消費電力の向上に貢献する。

この技術を用いた「Applied Endura Copper Barrier Seed IMS with Volta Ruthenium CVD」は、大手ロジックメーカーが採用。3nmノード向けに、供給を開始した。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

先端ロジック/メモリチップのパターニングには計測技術のブレークスルーが必要

先端ロジック/メモリチップのパターニングには計測技術のブレークスルーが必要

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回は、半導体の微細化が進展する中で求められている計測技術のブレークスルーについて紹介する。 第4のコンピューティング時代に求められるのは先端ロジック・メモリチップだけではない

第4のコンピューティング時代に求められるのは先端ロジック・メモリチップだけではない

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回は、同社のMaster Classイベントで発表されたヘテロジニアスデザインと先進のパッケージング技術についてさらに掘り下げる。 新リソグラフィ技術「DLT」を3Dパッケージ基板へ、AMATとウシオ電機が協業

新リソグラフィ技術「DLT」を3Dパッケージ基板へ、AMATとウシオ電機が協業

アプライド マテリアルズ(AMAT)とウシオ電機が、3Dパッケージ基板向けのリソグラフィ技術「DLT(Digital Lithography Technology)」について説明した。 シリコンカーバイド(SiC)が電気自動車の普及に拍車

シリコンカーバイド(SiC)が電気自動車の普及に拍車

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回のテーマは電気自動車への搭載が進むSiCデバイスだ。 半導体イノベーションを支えるのは先端技術だけではない

半導体イノベーションを支えるのは先端技術だけではない

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回は、同社のMaster Classイベントの開催と絡めて、ICAPS(IoT、通信、自動車、パワー、センサー)分野の動向について紹介する。