700Gbps超/590nsのデータ圧縮通信技術、FPGAクラスタの通信ボトルネックを解消:組み込み開発ニュース

国立情報学研究所らは、FPGAクラスタの通信性能を大幅に向上させる超低遅延、高帯域圧縮通信技術を開発した。圧縮、復号処理を含めた通信遅延を590nsに抑えつつ、最大757Gbpsの実効通信帯域を達成した。

国立情報学研究所は2026年3月5日、広島大学、富士通と共同で、FPGAクラスタにおける通信ボトルネックを解消する、超低遅延かつ高帯域なデータ圧縮通信技術を開発したと発表した。

同技術は、FPGA間のデータ伝送において、圧縮、復号処理を含めた通信遅延を590nsに抑えつつ、最大757Gbpsの実効通信帯域を達成。これにより、通信性能が制約となっていたFPGAベースの高性能計算システムのスケーラビリティを向上させる。

近年、特定の処理を高速かつ省電力に並列実行できるFPGAクラスタが注目されている。単体カードの計算やメモリ性能は向上しているが、大規模なAI(人工知能)学習などで多用される集合通信において、FPGA間の通信帯域や遅延がシステム全体の性能を左右する要因となっていた。従来のデータ圧縮方式はハードウェア実装が複雑で、処理遅延が増大するため、超低遅延を求める通信には適していなかった。

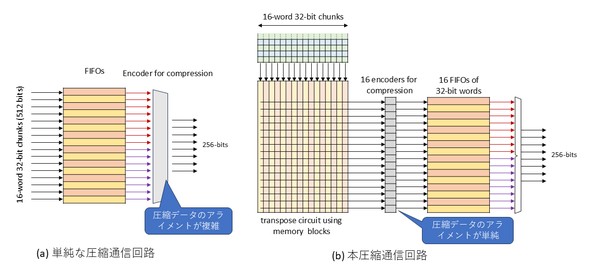

開発された技術は、データの膨張を防ぐ軽量な圧縮方式と、通信路の幅に合わせてデータを整列させる独自の回路構成を組み合わせている。具体的には、入力データの並び順を入れ替えることで複数のデータを同時に並列圧縮し、圧縮後のデータを通信路の幅にそろえて効率的に送り出す。この例の回路を用いた評価では、非圧縮時と比較して通信性能を約2倍に高めながら、遅延をサブμs以下に抑えることに成功した。

光技術を用いた高速通信回線を備えるFPGAクラスタでの評価では、AIの分散学習に用いる勾配データの通信に適用し、学習精度への影響がほとんどないことを確認した。今後は適応的な誤差制御や多様な数値表現への拡張を進め、将来の光インターコネクトを用いた高性能計算システムやAIアクセラレータへの展開を目指す。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

いまさら聞けない FPGA入門

いまさら聞けない FPGA入門

あなたは、人に「FPGA」を正しく説明できるだろうか? いまや常識となりつつあるFPGAについて、あらためてその概念から仕組み、最新動向までを解説する。(編集部) FPGAの特徴とは? 他デバイスと比較してみよう

FPGAの特徴とは? 他デバイスと比較してみよう

MONOistの人気解説記事「いまさら聞けないFPGA入門」が公開された2006年9月から10年以上が経過し、FPGAを取り巻く状況も大きく変わっています。そこで、あらためてFPGAの基礎から最近の動向までを含めて解説する「新・いまさら聞けないFPGA入門」を公開します。前編は、FPGAの特徴について、ASICやASSP、GPU、CPUと比較して説明します。 FPGAの力を引き出す3種の開発ツールとは

FPGAの力を引き出す3種の開発ツールとは

あらためてFPGAの基礎から最近の動向までを含めて解説する「新・いまさら聞けないFPGA入門」。後編は、FPGAの最大の特徴を引き出すのに用いる最新のツールと、FPGAの採用が広がっている新たな市場について紹介します。 深層学習を活用し、眼底画像から個人の血圧や血糖値を推定するAIモデルを公開

深層学習を活用し、眼底画像から個人の血圧や血糖値を推定するAIモデルを公開

国立情報学研究所は、学会主導データベース「Japan Ocular Imaging Registry: JOIR」で収集した画像データを活用し、眼底画像から個人の血圧や血糖値を推定するAIを開発した。Webサイトから無償でダウンロードできる。 自動運転車のISO34502危険シナリオ群を数学的に定式化

自動運転車のISO34502危険シナリオ群を数学的に定式化

国立情報学研究所アーキテクチャ科学研究系教授の蓮尾一郎氏と、京都大学大学院情報学研究科助教の和賀正樹氏らの研究グループが、ISO 34502の危険シナリオ群について、その意味内容を数学的に定式化した。 CNTセンサーとCVにより、検査物の構造を非破壊で3次元立体的に推定

CNTセンサーとCVにより、検査物の構造を非破壊で3次元立体的に推定

中央大学と国立情報学研究所は、検査物の内部材質と内部構造を非破壊で推定する新たな検査技術を開発した。カーボンナノチューブをセンサーに用いた材質同定型デバイスシステムと構造復元手法を組み合わせた。