プログラマブルロジックの誕生――CPLD前史:プログラマブルロジック本紀(1)(3/3 ページ)

FPGAに代表されるプログラマブルロジックICの歴史をたどる本連載。第1回は、プログラマブルロジックが誕生した1970年代の状況や、PLDのご先祖様となるPLAについて紹介する。【訂正あり】

PLDのご先祖様であるPLAの登場

それではPROMよりもう少し自由に使えるものはなかったのだろうか。そこで、最初に世の中に出て来たPLDとなるのがPLA(Programmable Logic Array)である。

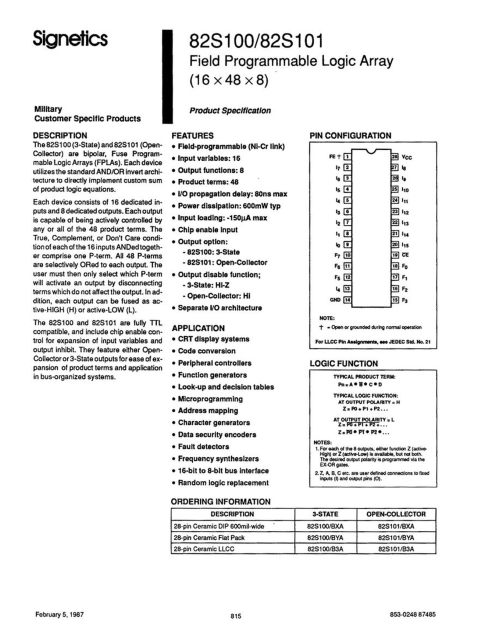

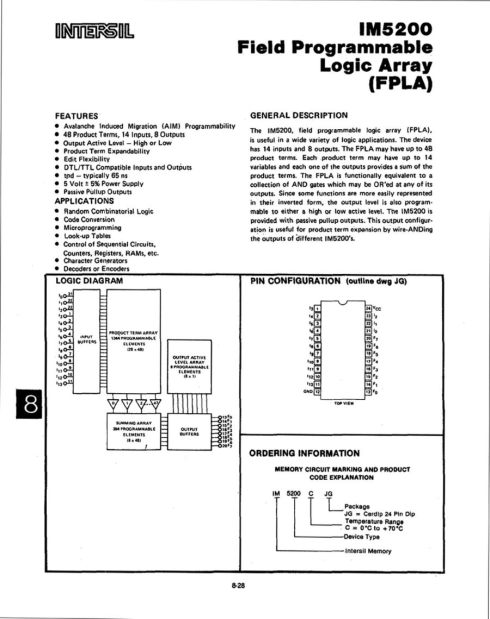

1975年、英Signeticの82S100 FPLA(図3)と、Intersil IM5200 FPLA(図4)という2種類のPLAが世の中に登場した。82S100は16入力/8出力、IM5200は14入力/8出力のプログラマブルロジックである。

図5 IntersilのIM5200 FPLAのデータシート。ちょっと図版が見えにくくなっているが、上側がProgrammable AND array、下側がProgrammable OR arrayとなっている[クリックで拡大] 出所:Intersil

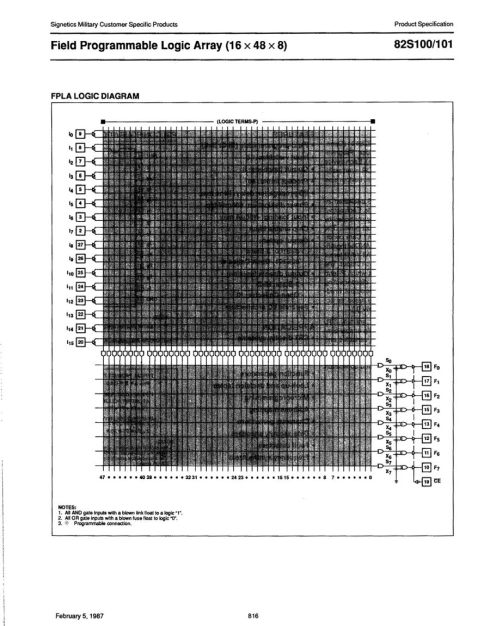

82S100の内部構造は図5に示す通りだ。IM5200も図4の左下に概略があるが、どちらも図3とよく似ている。

ただし、以下のように相違点も大きい。

- 上側のAND arrayがプログラマブルである

- AND arrayとOR array(図3におけるPROMのデコーダー部)をつなぐ部分は48個分しかない

そもそもPROMのAND arrayがFixedなのは、11ビット入力をフルにデコードできる(というかデコードできないとPROMにならない)から、そもそもプログラマブルである必要がない。PLAではデコードできるパターンは最大48に限られ(というか限るためにプログラムが必要である)、その結果を8ビットで出力できる形になっている。パッケージは82S100が600milの28端子DIP、IM5200が600milの24端子DIPであるが、どちらも5V単一電源で動作する。レイテンシは82S100が定格35ns/最大80ns、82S100が定格65ns/最大100nsとなっており、どちらもPROMに比べて圧倒的に高速である。

82S100とIM5200の内部構造は割と異なる(82S100はSigneticsのPROM技術を応用したもの、IM5200はIntersilのアバランチ誘起移動PROMプロセスを応用したもの)し、使い方も微妙に違うし、プログラミング環境も別だ。とはいえ、PROMを除くとこれら2社のPLAが、PLDのご先祖様ということになるだろう。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- 連載「プログラマブルロジック本紀」バックナンバー

いま振り返るFPGA普及・発展の歴史 〜日本上陸からおよそ20年〜

いま振り返るFPGA普及・発展の歴史 〜日本上陸からおよそ20年〜

FPGAに関するさまざまなテーマをお届けする本連載。記念すべき第1回はFPGAの概要と各年代のエポックメイキング、そして最新動向を紹介する ASICとFPGAの対比で見る“転換点”

ASICとFPGAの対比で見る“転換点”

ASICとFPGAが迎えた本格的な転換点とは? 双方の特長を踏まえたうえで、半導体製造プロセスにおけるテクノロジ・ギャップについて解説する いまさら聞けない FPGA入門

いまさら聞けない FPGA入門

あなたは、人に「FPGA」を正しく説明できるだろうか? いまや常識となりつつあるFPGAについて、あらためてその概念から仕組み、最新動向までを解説する。(編集部) FPGAの特徴とは? 他デバイスと比較してみよう

FPGAの特徴とは? 他デバイスと比較してみよう

MONOistの人気解説記事「いまさら聞けないFPGA入門」が公開された2006年9月から10年以上が経過し、FPGAを取り巻く状況も大きく変わっています。そこで、あらためてFPGAの基礎から最近の動向までを含めて解説する「新・いまさら聞けないFPGA入門」を公開します。前編は、FPGAの特徴について、ASICやASSP、GPU、CPUと比較して説明します。 FPGAの力を引き出す3種の開発ツールとは

FPGAの力を引き出す3種の開発ツールとは

あらためてFPGAの基礎から最近の動向までを含めて解説する「新・いまさら聞けないFPGA入門」。後編は、FPGAの最大の特徴を引き出すのに用いる最新のツールと、FPGAの採用が広がっている新たな市場について紹介します。