プログラマブルロジックの誕生――CPLD前史:プログラマブルロジック本紀(1)(2/3 ページ)

FPGAに代表されるプログラマブルロジックICの歴史をたどる本連載。第1回は、プログラマブルロジックが誕生した1970年代の状況や、PLDのご先祖様となるPLAについて紹介する。【訂正あり】

自由に内部の処理を変更できるICにはPROMがあったが……

まぁこうした場合、定番品を組み合わせて何とかするパターンが多い。しかし、結果的にTTL ICの数が不必要に増えてしまって回路が大きくなり、これに伴いタイミングが間に合わなくなったり基板が大型化したり、さらには原価が上がったりといった弊害が出る場合もあった。自由に内部の処理を変更できるようなTTL ICが存在すれば話は解決するのだが、そういう都合の良いものはなかなかなかった。

この「自由に内部の処理を変更できる」ICとして最初に利用されたのはPROM(Programmable ROM)である。PROMそのものは1956年に発明されており、1970年代後半だと5V単一電源で使えるIntelの2716(16Kビット UV EPROM)やその互換品が広く入手可能になっていた。

【訂正】初出時、本文中で「Intelの2706」と記載しましたが「Intelの2716」の誤りでした。2716の入力についても、本文中と図2、図3で「A0〜A11」と記載しましたが「A0〜A10」の誤りでした。併せて、入力数も12ビットから11ビットに減るため関連の記載も修正しております。おわびして訂正いたします[編集部/2025年8月15日午後21時40分]

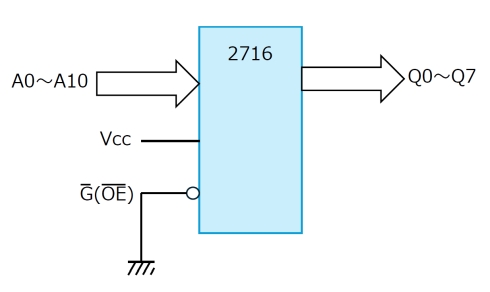

使い方は簡単で、あらかじめ2716の中にデータを書き込んでおき、あとはG(OE:Output Enabled)をGNDに落とした上でつなぐだけである。この場合A0〜A10のアドレスが入力、Q0〜Q7のデータが出力になり、11ビット入力、8ビット出力のロジック回路に化けるわけだ(図2)。

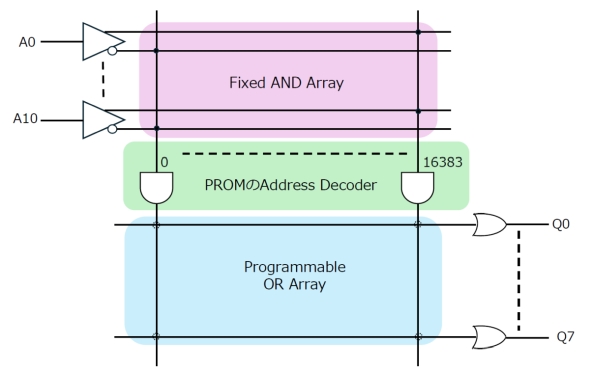

このPROMの等価回路が図3である。A0〜A10はまずFixed AND Arrayを経由し、その結果が(PROMのAddress Decoder経由で)アドレスとしてProgrammable OR Arrayに渡される。PROMに書き込んだデータというのは、要するにアドレスに対する出力のビットパターンをORの形で記録しているので、これがQ0〜Q7に引き渡されるというわけだ。

このように、ある程度大きな規模のロジックをまとめて実装するのにPROMは結構便利といえば便利なのだが欠点も多かった。オリジナルの2716がアクセス450ns、高速版の2716-1が350nsほどになっており、これは結構遅い。というのは2入力NANDが4つ入ったSN7400だとtPLH/tPHL(入力に応じて出力が変化するまでの時間)がだいたい10ns程度なので、SN7400を35〜45個並べたのに等しい遅延が発生するからだ。

価格面でも、当時のTTL ICが(購入量次第ではあるが)1米ドル未満なのが普通であり、一方2716は4米ドルと高価だった。価格面で比較しようとすると、おおむね7〜8個のTTL ICを置き換えられないと価格が折り合わないことになる。

PROMは使いにくいという問題もあった。11入力/8出力というのはちょっと普通のロジック回路では使わない規模である。もちろんROMに書き込むデータを工夫すれば、例えば6入力/4出力と5入力/4出力、3入力/2出力を3組といった使い方も可能ではあるのだが、ROMの容量を使い切るほどのパターンになるのは結構珍しい。そんなこともあって、ロジック回路の一部としてPROMを使うというケースは割とまれで、パターンジェネレータやデータコンバーターなど、ロジックというよりもテーブルルックアップ的に使うのが一般的であった。

Copyright © ITmedia, Inc. All Rights Reserved.