NVIDIAとTSMCが2nm以降の半導体製造をAIで最適化、計算リソグラフィが40倍高速に:FAニュース

NVIDIAは「GTC 2023」において、2nm以降の半導体製造を可能にする計算リソグラフィ向けのAIライブラリ「cuLitho」を、ASML、TSMC、シノプシスの3社と共同開発していることを明らかにした。

NVIDIAは2023年3月21日(現地時間)、オンラインで開催中のユーザーイベント「GTC(GPU Technology Conference) 2023」(開催期間:同年3月20〜23日)において、2nm以降の半導体製造を可能にする計算(Computation)リソグラフィ向けのAI(人工知能)ライブラリ「cuLitho」を、ASML、TSMC、シノプシス(Synopsys)の3社と共同開発していることを明らかにした。TSMCは、同年6月からcuLithoを用いての半導体製造を開始する計画である。

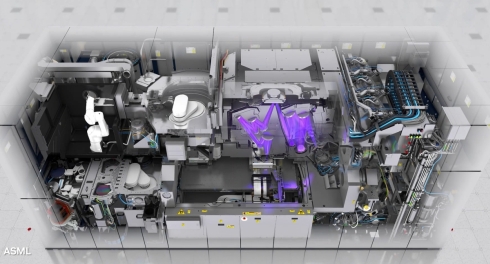

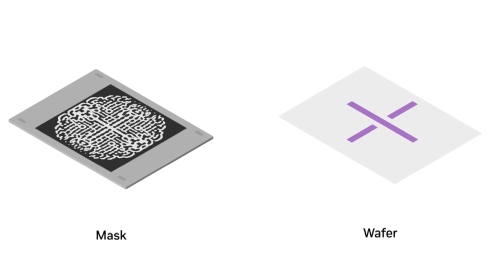

半導体製造の最初のプロセスとなるリソグラフィ工程では、フォトマスクの作成と、フォトマスクに光を照射してのパターン転写から構成されている。NVIDIA 創業者兼CEOのジェンスン・フアン(Jensen Huang)氏は「これらは物理学の限界ギリギリのところで画像を処理する作業である」と説明する。特に、最先端の半導体製造のリソグラフィ工程に用いられるEUV(極端紫外光)システムでは、スズにレーザーを毎秒5万回当てて気化させることで波長13.5nmのEUV光を放射するプラズマを生成し、複数の鏡から構成される光学系の中に組み込まれたフォトマスクに作り込まれた回路構造を、シリコンウエハー上に塗布されたフォトレジストに3nmという微細な回路パターンとして転写する。「ウエハーは4分の1nm以内に位置調整され、あらゆる振動に合わせて毎秒2万回調整されている」(フアン氏)という。

また、回路パターン転写の原板となるフォトマスクは、波長13.5nmの光の干渉に基づく物理アルゴリズムに基づいてフォトマスク上のパターンが作成される。実際のフォトマスク上のパターンは、転写される回路パターンとは全く異なるものになる。さらに、光学系を通過した光がフォトレジストと相互作用する際の挙動も考慮しなければ、正確な回路パターンの転写は実現できない。

これらリソグラフィ工程を円滑に実現するための計算リソグラフィは、半導体の設計と製造における最大の計算ワークロードである。フアン氏は「年間数十億単位のCPU時間を消費しており、大規模なデータセンターが年中無休で稼働してフォトマスクを作っている」と指摘する。これらのデータセンターも、先端半導体工場の建設に必要なインフラであり、兆円単位という設備投資金額の一部になっている。

今回発表したcuLithoは、NVIDIAの最新GPUとAI技術を活用して計算リソグラフィを40倍以上高速化するものだ。NVIDIAとTSMC、EUVシステムを手掛けるASML、EDA(電子設計自動化)ツール大手のシノプシスが約4年をかけて開発した。

例えば、TSMCで製造されているNVIDIAの最新GPUチップ「H100」は89枚のフォトマスクを用いている。CPUベースの計算リソグラフィでは、フォトマスクを1枚作成するのに2週間かかっていた。GPUとAI技術を活用するcuLithoであれば、1枚作成するのに8時間で済む。TSMCは、500台のAI演算用サーバ「DGX H100」により、これまで計算リソグラフィに用いられてきた4万台のCPUサーバを代替でき、消費電力も35MWから5MWに削減できるという。

フアン氏は「TSMCはcuLithoによって、試作にかかる時間を短縮してスループットを向上させ、消費電力の削減によりCO2排出量も削減した上で、2nm以降の半導体製造に対応できるだろう」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

NVIDIAがAda LovelaceアーキテクチャでRTXを第3世代に、Jetson NanoもOrin世代へ

NVIDIAがAda LovelaceアーキテクチャでRTXを第3世代に、Jetson NanoもOrin世代へ

NVIDIAは、ユーザーイベント「GTC September 2022」の基調講演において、新たなGPUアーキテクチャ「Ada Lovelaceアーキテクチャ」を発表するとともに、同アーキテクチャを採用したプロフェッショナル/コンシューマー向けGPUプラットフォーム「RTX」の第3世代品を投入することを明らかにした。 NVIDIAが新GPUアーキテクチャ「Hopper」を発表、AI処理性能は4000TFLOPSへ

NVIDIAが新GPUアーキテクチャ「Hopper」を発表、AI処理性能は4000TFLOPSへ

NVIDIAは「GTC 2022」の基調講演において、新たなGPUアーキテクチャである「NVIDIA Hopperアーキテクチャ」と、Hopperを搭載するGPU「NVIDIA H100 GPU」を発表。H100は、800億ものトランジスタを集積しており、自然言語認識AIの開発で用いられているトランスフォーマーモデルの精度を落とすことなく処理性能を大幅に向上できるという。 なぜ日本で2nmの先端ロジック半導体を製造しなければならないのか

なぜ日本で2nmの先端ロジック半導体を製造しなければならないのか

半導体などマイクロエレクトロニクス製造サプライチェーンの国際展示会「SEMICON Japan 2022」が2022年12月14日に開幕し、オープニングキーノートパネルとして、新たな半導体製造会社であるRapidusなども含む「半導体・デジタル産業戦略」に深く関わる主要メンバーが登壇し「グローバルリーダーを目指す産官学戦略」をテーマに、日本における半導体産業の在り方や社会変革の方向性などについて語った。 2nm以降世代に向けた半導体プロジェクトが始動、かつての国プロとの違いとは

2nm以降世代に向けた半導体プロジェクトが始動、かつての国プロとの違いとは

NEDOと経済産業省、AIST、TIAの4者が「先端半導体製造技術つくば拠点オープニングシンポジウム」を開催。「ポスト5G情報通信システム基盤強化研究開発事業」の中で進められる「先端半導体製造技術の開発」のキックオフに当たるイベントで、2nm世代以降のロジックICを対象とした前工程プロジェクトと、3D ICを対象とした後工程プロジェクトについての説明が行われた。 RapidusとIBMが2nm半導体の量産へ協力、日本の半導体産業に期待寄せる

RapidusとIBMが2nm半導体の量産へ協力、日本の半導体産業に期待寄せる

IBMとRapidus(ラピダス)は2022年12月13日、東京都内で会見を開き、半導体の微細化技術の発展に向けた共同開発パートナーシップを締結したと発表した。 2nm半導体の国産目指すRapidusとベルギーのimecが協業へ、覚書を締結

2nm半導体の国産目指すRapidusとベルギーのimecが協業へ、覚書を締結

2nmプロセスの半導体の量産を目指す新設半導体企業であるRapidusと、ベルギーの半導体研究開発機関であるimecは2022年12月6日、先端半導体技術の研究開発において、長期的かつ持続的な協力関係を構築するためMOC(協力覚書)を締結したと発表した 性能とエネルギー効率に優れた2nmチップ技術を発表

性能とエネルギー効率に優れた2nmチップ技術を発表

IBMは、2nmのナノシート技術による新しい半導体デザインを発表した。指の爪ほどのチップに最大500億個のトランジスタを搭載可能で、7nmノードチップと比べて性能が45%向上し、エネルギー消費量を75%削減する。