NVIDIAが新GPUアーキテクチャ「Hopper」を発表、AI処理性能は4000TFLOPSへ:組み込み開発ニュース(1/2 ページ)

NVIDIAは「GTC 2022」の基調講演において、新たなGPUアーキテクチャである「NVIDIA Hopperアーキテクチャ」と、Hopperを搭載するGPU「NVIDIA H100 GPU」を発表。H100は、800億ものトランジスタを集積しており、自然言語認識AIの開発で用いられているトランスフォーマーモデルの精度を落とすことなく処理性能を大幅に向上できるという。

NVIDIAは2022年3月22日(現地時間)、オンラインで開催中のユーザーイベント「GTC(GPU Technology Conference) 2022」(開催期間:同年3月21〜24日)の基調講演において、新たなGPUアーキテクチャである「NVIDIA Hopperアーキテクチャ(以下、Hopperアーキテクチャ)」と、Hopperを搭載するGPU「NVIDIA H100 GPU(以下、H100)」を発表した。H100は、TSMCの「4Nプロセス」の採用により800億ものトランジスタを集積しており、前世代のGPU「NVIDIA A100 GPU(以下、A100)」と比べて自然言語認識AI(人工知能)の開発で用いられているトランスフォーマーモデルの精度を落とすことなく、処理性能を大幅に向上できるという。

また、2021年4月に発表したCPU製品「Grace」の新製品として、新たなチップ間高速インターコネクト技術「NVLink-C2C」でつなげた2つのCPUチップにArmの「Neoverse」ベースのプロセッサコアを144個集積した「Grace CPU Superchip」も発表した。このGrace CPU Superchipにより、NVIDIAはデータセンター向けCPU市場に本格的に参入することになる。

NVIDIA 創業者兼CEOのジェンスン・フアン(Jensen Huang)氏は「データセンターは今やAI工場と言っても過言ではない。大きな性能の飛躍を遂げたH100は、世界のAIインフラの新たなエンジンとなるだろう」と強調する。

Hopperアーキテクチャを構成する6つの技術

Hopperアーキテクチャは、従来の機械学習モデルよりもはるかに計算リソースが求められるトランスフォーマーモデルの処理能力を大幅に向上することを目標に開発された。ブレークスルーとなる技術としては、「世界最先端のチップ」「新たなトランスフォーマーエンジン」「第2世代のセキュアなマルチインスタンスGPU」「コンフィデンシャルコンピューティング」「第4世代NVIDA NVLink」「DPXインストラクション」の6つが挙げられている。

1つ目の「世界最先端のチップ」では、TSMCの最先端プロセスである「4Nプロセス」を採用して800億ものトランジスタを集積してAI処理能力の向上を図るとともに、システム規模を拡大する際に求められるメモリバスやインターコネクトなどに最新技術を採用して帯域幅を向上している。

H100のAI処理性能は、Hopperアーキテクチャから新たに導入した演算精度のFP8(8ビット浮動小数点演算)で4000TFLOPSを実現した。これは、前世代であるA100の演算精度FP16と比べて6倍に当たる。なお、FP16で2000TFLOPS、TF32で1000TFLOPS、FP64で60TFLOPSとなっており、これらはA100のAI処理性能の3倍となっている。メモリバスでは帯域幅が3GB/sのHBM3を初めて実用化し、外部とのインターコネクトでは128GB/sのPCI Gen5、900GB/sの第4世代NVIDIA NVLinkを採用。外部接続の帯域幅の総計は4.9TB/sに達するという。また、消費電力についてはTDP(熱設計電力)で700Wとしている。

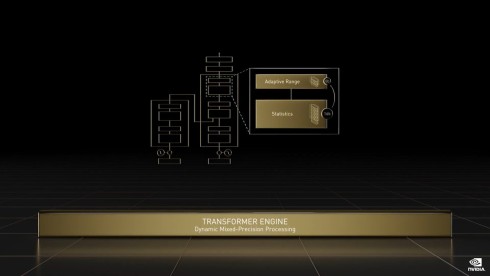

2つ目の「新たなトランスフォーマーエンジン」では、Voltaアーキテクチャから採用しているAIの処理に最適なTensorコアが第4世代となり、自然言語認識AIに用いられるトランスフォーマーモデルをより高速に処理できる仕組みを取り入れた。先述した演算精度FP8の4000TFLOPSという性能は、この新たなトランスフォーマーエンジンによるものだ。

3つ目の「第2世代のセキュアなマルチインスタンスGPU」は、前世代のAmpereアーキテクチャから採用している、1つのGPUを最大で7つの独立したGPUに分離して扱えるマルチインスタンスGPU(MIG)を、クラウド上で利用できるようにセキュアなマルチテナント構成で利用できるように進化させたものだ。

Copyright © ITmedia, Inc. All Rights Reserved.