ポスト「京」のプロセッサ「A64FX」はArmベースながら異彩放つ重厚系:Arm最新動向報告(5)(3/3 ページ)

「Arm TechCon 2018」では、Armのアーキテクチャライセンスを基に開発が進められている、次世代スーパーコンピュータのポスト「京」(Post-K)向けのプロセッサ「A64FX」に関する講演が行われた。

インターコネクト「Tofu」も進化

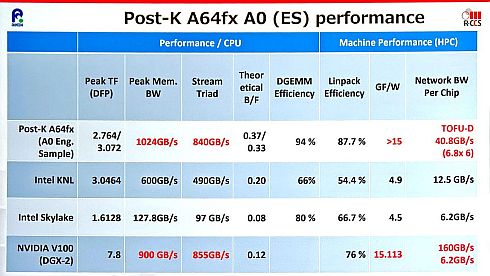

さて、ここまでのスライドはHotChips 30と共通だったが、ここからアップデートを。2018年10月の時点で既にA0サンプルのA64FXが稼働しており、それを利用しての実測値がこちら(図11)である。動作周波数は明らかにされていないが、DPで2.764T/3.072TFLOPSという数字からすると1.8G/2GHz駆動と考えられる。もとになったSPARC XIfxは20nmプロセスで2.2GHz駆動だったから、これに比べるとやや低めではあるが、そもそもA0サンプルということを考えれば、これでも十分な速度といえる。また、そもそも高密度に実装されることを考えると、あまり消費電力は増やしたくないわけで、それもあって低めに抑えられている可能性もある。

図11 ピーク演算性能がNVIDIAの「Tesla V100」に及ばないのは、そもそも演算器の数が全然違う(Tesla V100は最大構成で2688個のFP64の演算器を実装している)ためだ。しかし、汎用プロセッサとしてはかなり高い性能である(クリックで拡大)

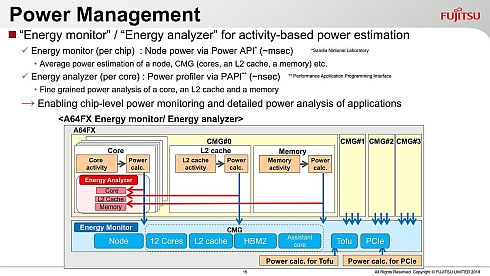

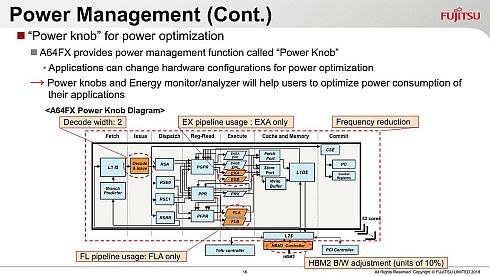

省電力関連で言えば、常に消費電力を監視しながら電力制御を行う仕組みは当然に入っている訳だが(図12)、消費電力を絞る方法として、従来のクロックゲーティングやパワーゲーティングに加え、デコード帯域を絞ったり、利用可能な実行ユニットを制限したりというパワーノブ(Power Knob)という方式も実装されていることが明らかにされた(図13)。

図13 デコードの命令数を絞る、という実装はあまり見かけない。もっとも、例えばx86だとデコード後の内部命令をL0命令キャッシュに相当するMicro Ops Cacheに蓄え、デコーダーを動かさないなんて仕組みも入っているので、単にデコードを絞ってもうまくいかない気もするが(クリックで拡大)

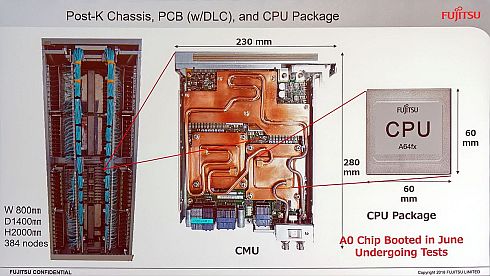

このA64FXプロセッサは1つのCMU(CPU Memory Unit)に2つずつ搭載され、このCMUを8枚搭載したBoB(Bunch of Brades)を3組まとめたシェルフを、1つのラックに8つ搭載する予定になっている。つまり、1ラックで384ノード、18432コアが実装される形となる(図14)。

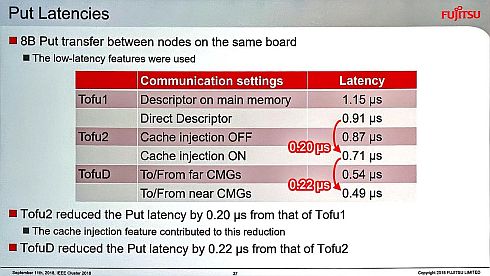

最後に「Tofu」関連について。富士通は「京」の立ち上げの際に、初代のTofu(Torus Fusion)というインターコネクトを採用したが、SPARC64 XIfx(Tofu2)を経てA64FXにも引き継がれており、こちらも「TofuD」に進化している。このTofuDで8バイトのデータを送る際のレイテンシ(遅延時間)を比較したのがこちら(図15)。大規模システムの場合、このインターコネクトのレイテンシが性能に与えるインパクトはかなりシビアなもので、少数のノードで動かすとベンチマークプログラムである「Linpack」の効率が80%超えなのに、同じシステムを大規模ノードに拡張したら50%程度まで落ちた、なんて話は珍しくもない。

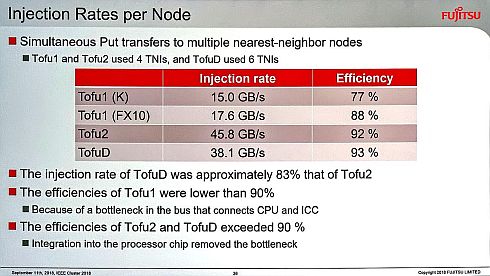

その理由は、ノード間の通信に時間がかかり過ぎるからで、これを最小限に抑えるためにもこのレイテンシ削減は大きな意味がある。もちろん帯域そのものも確実に広がっており(図16)、これで性能改善(というか性能劣化防止)に努めているという話である。

ということで、駆け足でA64FXの特徴をご紹介してきた。何というか、内部構造はArmのプロセッサというよりは富士通の従来の構造そのままで、むしろArmであることに違和感を覚えそうなほどだが、もう最近のプロセッサは(それこそx86はとっくにそうだし、IBMもZ系列なんかは特にそうだが)対応する命令セットと内部の構造にはあまり関係が無い(デコード段で命令変換を掛けてしまうので、それこそVILW(Very Long Instruction Word)でもない限り、大体処理できる)ことを端的に示しているといえる。

Armのコアがそもそも省電力向けを身上としており、Cortex-A76でもまだ例えばIntelの「Skylake」などに比べるとやや軽めに見えるのに対し、A64FXは明らかに重厚系のコアであって、会場でもちょっと異彩を放っていた感はあった。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- ≫連載「Arm最新動向報告」バックナンバー

スーパーコンピュータ京がGraph500で8期連続世界第1位を獲得

スーパーコンピュータ京がGraph500で8期連続世界第1位を獲得

理化学研究所らによる国際共同研究グループは、大規模グラフ解析に関するスーパーコンピュータの国際的な性能ランキングGraph500にて、スーパーコンピュータ「京」による解析結果が8期連続で第1位を獲得したと発表した。 AIや大規模解析では、省力化ではなく価値創出が重要

AIや大規模解析では、省力化ではなく価値創出が重要

エムエスシーソフトウェアが開催した年次ユーザーイベント「MSC Software 2018 Users Conference」において、筑波大学 システム情報系 教授で筑波大学 人工知能科学センター センター長、理化学研究所 計算化学研究機構客員研究員を務める櫻井鉄也氏が、デジタルとAI(人工知能)をキーワードに「AI技術を用いたデータとシミュレーションの統合活用」と題して講演した。 クルマづくりは分子レベルから、「材料をモデルベース開発」「最短5分で耐食試験」

クルマづくりは分子レベルから、「材料をモデルベース開発」「最短5分で耐食試験」

マツダのクルマづくりを支える先端材料研究を探る。モデルベース開発を応用した分子レベルでの素材開発や、耐食対策を効率化する短時間の防錆性能評価といった独自の取り組みを紹介する。 製造業の“みんなのスパコン”TSUBAMEのCAE利用の取り組みを聞く

製造業の“みんなのスパコン”TSUBAMEのCAE利用の取り組みを聞く

東工大は「みんなのスパコン」と銘打ち、スパコン「TSUBAME」の学外利用を積極的に推進してきた。企業の使いやすさを模索してきた東工大の取り組みや、スパコンが注目されている背景などについて紹介する。 スパコン「京」を使った設計が無料で試せる日がくる?

スパコン「京」を使った設計が無料で試せる日がくる?

東大生技研の小野謙二氏が取り組むスパコン京を活用した設計システム。2013年には企業が無料で利用できるようになる。