ポスト「京」のプロセッサ「A64FX」はArmベースながら異彩放つ重厚系:Arm最新動向報告(5)(2/3 ページ)

「Arm TechCon 2018」では、Armのアーキテクチャライセンスを基に開発が進められている、次世代スーパーコンピュータのポスト「京」(Post-K)向けのプロセッサ「A64FX」に関する講演が行われた。

AIやディープニューラルネットワークの処理も念頭に置く

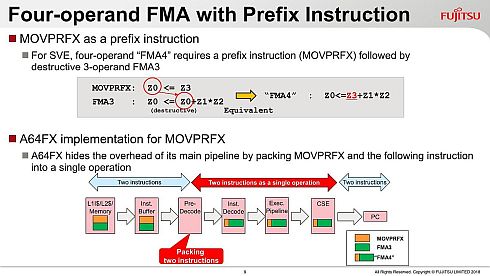

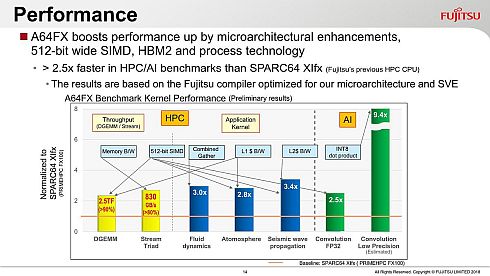

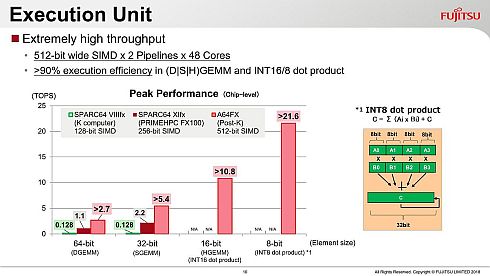

そのSVEであるが、FMA(Fused Multiply-Add)命令を実行しようとすると、本来は4オペランドのものを3オペランドで表現する必要があり、この結果、MOVPRFXとFMA3の2つの命令でFMA4を表現する形になっている(図5)。これをプレデコード(Pre-Decode)の段階で1命令として処理することで、FMAを1サイクルで処理可能にしている。こうした工夫もあり、このSIMDを使った場合の性能は、富士通の従来のSPARC系列に比べて大幅に性能が改善している(図6)。

図6 A64FXのアーキテクチャのベースはSPARC64 XIfxであるが、SIMD幅の拡張と動作周波数の向上、コア数の増加などで、64/32ビットの「DGEMM」でも2倍以上の性能が発揮できる(クリックで拡大)

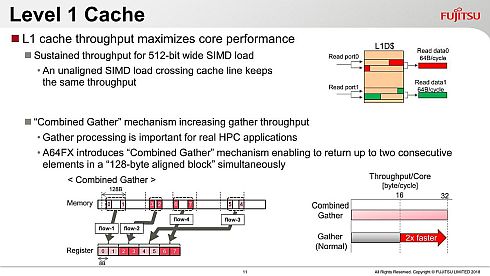

またA64FXでは、当初からAI(人工知能)やプレデコードを要するディープニューラルネットワークの処理を念頭に置いて8/16/32ビットの整数もサポートしており、これもあって特に8ビットの処理では20TOPS(1秒当たり20兆回の演算が可能)を超える性能を発揮できるとされる。これを支える仕組みの1つが、L1データキャッシュに搭載されるCombined Gather(図7)である。SIMD演算の場合、必ずしも必要なデータがキャッシュライン内に配されているとは限らず、キャッシュラインをまたいでデータをアクセスする必要があることも多い。この際に、2つのキャッシュラインを同時にアクセスすることで、キャッシュラインをまたいでも64バイト/サイクルのスループットを実現できるという仕組みである。

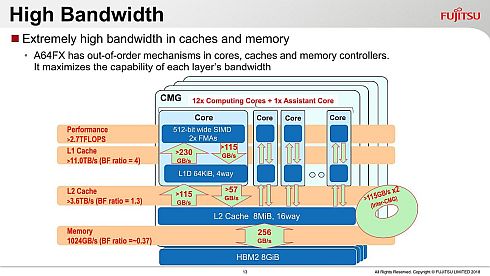

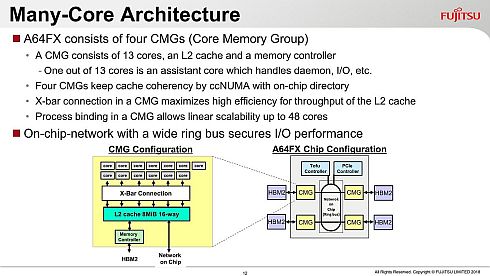

CMGの概略がこちら(図8)である。先述した通り、13コアのうち1コアはI/Oなど向けで、残り12コアが演算処理を担う。このCMGが4つ、オンチップネットワーク経由で接続されトータルで48コア(+4コア)の構成になる形だ。そのCMG内の帯域をまとめたのがこちら(図9)。L1キャッシュレベルでB/F比(Bytes/Flops比)が4、L2でも1.3という高い数字を示しているのが特徴的だ。さすがにHBM2まで行くと0.37まで落ちるので、プログラム側での最適化の配慮は必要だが、高いB/F比が要求されるアプリケーションでも性能を出す、という目的に沿った構成になっているのが分かる。

図8 ちなみに図には無いが、CMG当たりの8MBのL2キャッシュという容量はやや不足気味に感じるが、シミュレーションの結果これで足りる(というか、コストとかダイサイズとの兼ね合いで、このあたりを着地点としたそうだ)という話だった。おそらく、HBM2がこの外に付くので、L2そのものは8MB程度でもなんとかなるという話なのだと思う(クリックで拡大)

ちなみにその性能について言えば、HPC向けでどんな技術がどの分野に貢献しているかをまとめたのがこちら(図10)。性能比較のベースラインとなっているのが「SPARC64 XIfx」である。取りあえず一番効くのが512ビットSIMD、というこれはまぁ当然な話ではあるのだが。

Copyright © ITmedia, Inc. All Rights Reserved.