アルテラ、14nm世代に向けた開発環境「Quartus Prime」

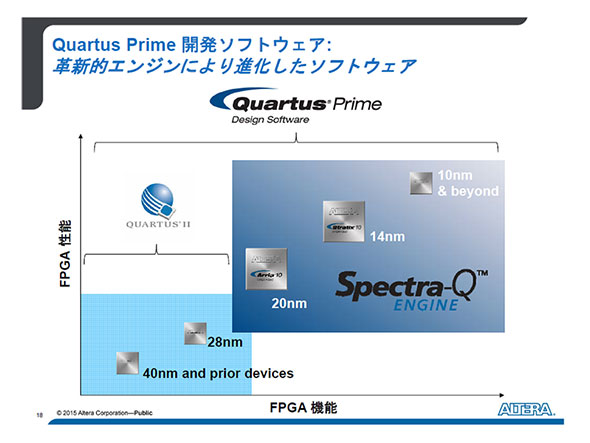

米Alteraは同社FPGA/SoC開発環境「Quartus II」の後継となる「Quartus Prime」を発表した。「Arria 10」や「Stratix 10」など20nm世代以降の製品をにらんだ設計がなされており、複雑化するFPGAの開発を高速に行える。

米Alteraは2015年11月2日(現地時間)、同社FPGA/SoC開発環境「Quartus II」の後継となる開発ソフトウェア「Quartus Prime」を発表した。既に提供は開始されており、同社Webサイトより入手できる。

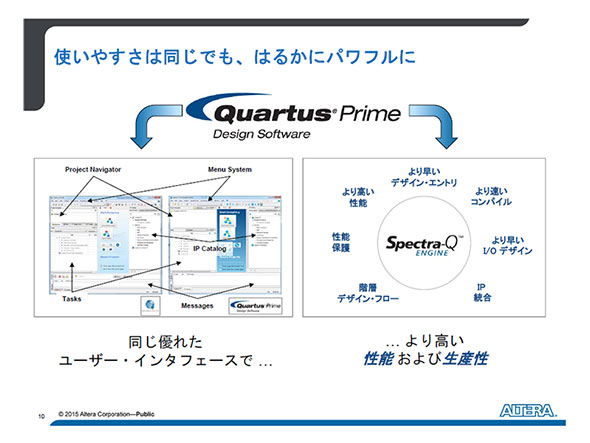

新製品は操作インタフェースこそ既存「Quartus II」を継承するが、Quartus II v 15.0と同時に登場した階層型データベース生成エンジン「Spectra-Q エンジン」をバックエンドに実装。対応した製品においては、配置アルゴリズムの最適化によって既存製品比で最大30%という高速化と、最大10倍のI/O設計高速化、4倍のコンパイル速度を実現する(Arria 10 SoCでの比較時)。

Quartus PrimeはQuartus IIの後継と位置付けされているが、最大の効果を発揮するのは20ナノメートルプロセス以下の製品(Arria 10ならびStratix 10、及び後継製品)であり、それ以前のプロセスルールを採用する製品については利用はできるものの、得られる効果が限定的なものとなるという。

製品は無償の「ライトエディション」(既存ウェブエディション相当)と有償の「スタンダードエディション」(既存サブスクリプションエディション相当)、「プロエディション」と3バージョンが用意される。最上位の「プロエディション」はArria 10以降の製品をターゲットとしており(MAX 10はサポートされない)、実装するSpectra-Q エンジンもArria 10以降の製品に最適されている。

System Verilog 2005およびVHDL 2008といった言語のサポート、規則チェック付きのリアルタイムI/O配置である「BluePrint Platform Designer」、コンパイル済IPおよびプラットフォームのインクリメンタル最適化である「Rapid Recompile」もプロエディションのみで利用できる機能となっている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

FPGAでのLチカをVerilog HDLで理解する

FPGAでのLチカをVerilog HDLで理解する

今回はFPGAでのLチカを例に、FPGA開発に必要なハードウェア記述言語の解説をしたい。用いる「Verilog HDL」はArduinoやCの経験がある方なら、理解そのものはそう難しくないと思う。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 「Stratix 10」詳細が発表、“どこでもレジスタ”で性能2倍

「Stratix 10」詳細が発表、“どこでもレジスタ”で性能2倍

アルテラがSoC FPGA「Stratix 10 FPGA & SoC」の詳細を公開した。配線遅延に対処する「HyperFlex」の導入などにより、コア性能2倍、最大70%の消費電力削減を実現する。 FPGAコンパイルを最大8倍高速化、「Quartus II」に新エンジン

FPGAコンパイルを最大8倍高速化、「Quartus II」に新エンジン

アルテラがFPGA開発環境「Quartus II」の最新版と最新版に対応する階層型データベース生成エンジン「Spectra-Q エンジン」を発表した。導入によってコンパイルを最大8倍高速化するとしている。 アルテラ、浮動小数点DSPサポートの「Quartus II 開発ソフトウェア v14.1」

アルテラ、浮動小数点DSPサポートの「Quartus II 開発ソフトウェア v14.1」

アルテラは開発ツール「Quartus II 開発ソフトウェア v14.1」を発表した。「Arria 10 SoC」が実装する浮動小数点DSPブロックをサポートしており、最大1.5TFLOPSのDSP性能を得ることが可能になる。 アルテラ、コンパイルを高速化した「Quartus II Arria 10」新バージョン

アルテラ、コンパイルを高速化した「Quartus II Arria 10」新バージョン

アルテラは20nm FPGA/SoC用の開発ソフト「Quartus II 開発ソフトウェア Arria 10 エディション v14.0」を発表した。競合する他社20nmツールに比べ、平均2倍以上のコンパイル速度を実現するという。