RISC-Vとチップレットで“高性能”を設計、ジム・ケラー氏率いるテンストレント:組み込み開発ニュース(2/2 ページ)

AIアクセラレータやRISC-VベースのCPU、チップレット技術を手掛けるテンストレント(Tenstorrent)の日本法人・テンストレント・ジャパンが、同社のプロダクトや事業戦略などについて説明した。

8命令デコードの「Ascalon」をベースにIPのスケーラビリティを確保

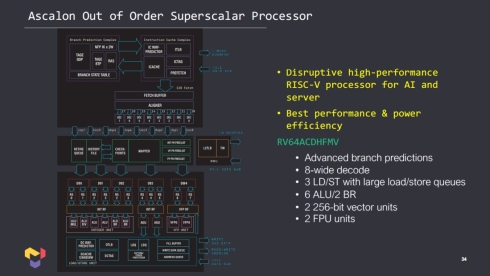

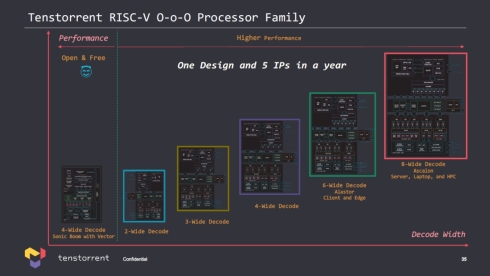

RISC-VベースCPUとして展開する「Ascalon」は、HPC(高性能コンピューティング)をはじめとする高性能処理向けのIPプロダクトとなっている。Ascalonは8命令デコードを特徴としているが、命令デコード数を6、4、3、2と減らすことで、ユーザーの求める処理性能に対応するIPのラインアップを1年以内に5つまで広げる方針だ。

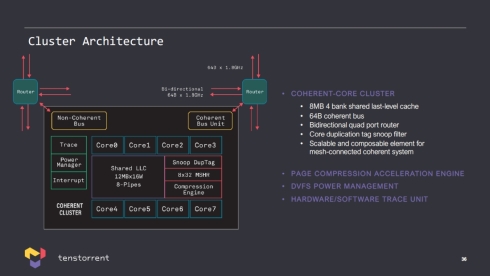

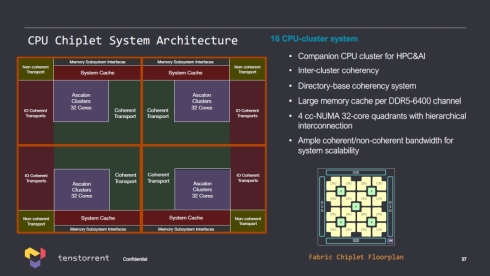

また、CPUの通信制御では、チップ間やメモリとの接続に用いるコヒーレントバスユニットと、外部インタフェースなどとつなぐ非コヒーレントバスユニットを用意することでスケーラビリティを確保している。これらの特徴をチップレット技術と組み合わせれば、より大規模なCPUクラスタシステムを構築することも容易になる。

チップレット技術としては、FPGAやCPU、AIアクセラレータなどの計算処理ユニットの他、イーサネットやPCI-Express、メモリインタフェースなどのI/Oだけでなく、サードパーティーIPや顧客自身のIPなどについても最適にチップレットとして活用できるようにするという。中野氏は「高性能を設計するという意味合いでは、共同設計(Co-Design)という方向性も打ち出しており、設計の最終段階であるテープアウトまで伴走することが可能だ」と強調する。また、Ascalonへのチップレット技術の適用を拡大することで、「Ageis」と呼ぶHPCプロセッシングノードの形での提案も進めているという。

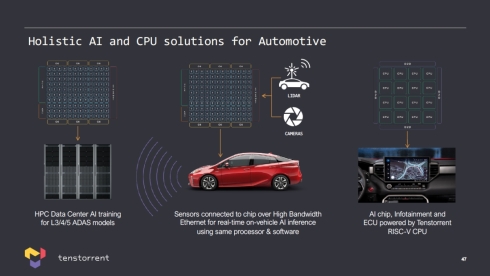

AIアクセラレータとRISC-VベースCPUも高性能が特徴であるため、現時点での評価の中心はHPCやエンタープライズ系システムなどだ。しかし、今回の日本法人の設立によって、より強く意識しているのが自動車向けでの展開である。自動運転システムにおけるカメラとLiDAR(Light Detection and Ranging、ライダー)のセンサーフュージョン処理でAIアクセラレータが、インフォテインメントユニットなどでRISC-VベースCPUの採用が期待できるという。「2024年後半以降に向けて、低消費電力低コストを特徴とするAIアクセラレータのQuasarやRISC-VベースCPUの採用を目指したい」(中野氏)としている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

RISC-Vへの移行の流れは止まらない、「2024年にはArmを超える」

RISC-Vへの移行の流れは止まらない、「2024年にはArmを超える」

SiFive Japanは、SiFive米国本社で共同設立者・主任設計技術者を務めるクルスト・アサノヴィッチ氏の来日会見を開いた。同氏は「業界は常に高品質のオープンスタンダードを求めており、プロセッサもRISC-Vへの移行が進めば元に戻ることはない」と強調した。 「今こそRISC-V浸透のベストタイミング」、SiFiveが日本法人を設立

「今こそRISC-V浸透のベストタイミング」、SiFiveが日本法人を設立

オープンソースのプロセッサコア「RISC-V」に基づく半導体IPプロダクトを展開するSiFiveが、日本法人「SiFive Japan株式会社」の設立を発表した。2022年8月に法人登記を完了する予定で、代表取締役社長には、ザイリンクス日本法人の社長を務め、スパンションやAMDの日本法人でも活躍してきたサム・ローガン氏が就任する。 ルネサスが64ビットRISC-Vコア搭載製品を発表、ローエンド汎用MPUの「RZ/Five」

ルネサスが64ビットRISC-Vコア搭載製品を発表、ローエンド汎用MPUの「RZ/Five」

ルネサス エレクトロニクスがオープンソースISA(命令セットアーキテクチャ)である「RISC-V」を採用した汎用MPU「RZ/Five」を発表。同社は、64ビットのRISC-V CPUを搭載する汎用MPUの開発は世界に先駆けた取り組みになるとしている。 ルネサスがRISC-V採用、ArmやRXベースの製品もある産業機器向け32ビット製品で

ルネサスがRISC-V採用、ArmやRXベースの製品もある産業機器向け32ビット製品で

ルネサス エレクトロニクスは、オープンソースのプロセッサコアIPである「RISC-V」を用いた組み込みCPUコアや関連するSoC開発環境のサプライヤーである台湾のアンデスとの技術提携を発表した。ルネサスは新開発のASSPにアンデスのRISC-Vベースの32ビットCPUコアである「AndesCore」を組み込み、2021年下半期にサンプル提供を開始する。 実効効率で世界トップクラスのエッジAIプロセッサアーキテクチャ、東工大が開発

実効効率で世界トップクラスのエッジAIプロセッサアーキテクチャ、東工大が開発

NEDOと東京工業大学は、エッジ機器で高効率なCNN(畳み込みニューラルネットワーク)による推論処理が可能なプロセッサアーキテクチャを開発したと発表した。同プロセッサアーキテクチャに基づく大規模集積回路(LSI)も試作し、「世界トップレベル」となる消費電力1W当たりの処理速度で最大26.5TOPSという実効効率を確認している。 Arm「Custom Instruction」の衝撃、RISC-Vへの徹底抗戦を貫く

Arm「Custom Instruction」の衝撃、RISC-Vへの徹底抗戦を貫く

2019年10月6〜8日にかけてArmが年次イベント「Arm TechCon 2019」を開催した。本連載では、同イベントの発表内容をピックアップする形で同社の最新動向について報告する。まずは、Armのこれまでの方針を大転換することとなった、ユーザーに独自命令を組み込むことを許す「Custom Instruction」について紹介しよう。