実効効率で世界トップクラスのエッジAIプロセッサアーキテクチャ、東工大が開発:人工知能ニュース

NEDOと東京工業大学は、エッジ機器で高効率なCNN(畳み込みニューラルネットワーク)による推論処理が可能なプロセッサアーキテクチャを開発したと発表した。同プロセッサアーキテクチャに基づく大規模集積回路(LSI)も試作し、「世界トップレベル」となる消費電力1W当たりの処理速度で最大26.5TOPSという実効効率を確認している。

NEDO(新エネルギー・産業技術総合開発機構)と東京工業大学は2021年8月23日、エッジ機器で高効率なCNN(畳み込みニューラルネットワーク)による推論処理が可能なプロセッサアーキテクチャを開発したと発表した。同プロセッサアーキテクチャに基づく大規模集積回路(LSI)も試作し、「世界トップレベル」(ニュースリリースより)となる消費電力1W当たりの処理速度で最大26.5TOPSという実効効率を確認している。今後は、スマートフォンの先進的なAR(拡張現実)アプリケーションやロボットの柔軟な動作制御など、電力供給量などの制約が厳しいエッジ機器における高度なリアルタイムAI(人工知能)処理を単独実行する用途に向け、推論処理のさらなる高精度化やRISC-Vプロセッサなどとのシステムレベル統合を進める方針だ。

深層学習技術の発展により、CNNに基づくAIアルゴリズムの推論処理の応用範囲が広がっているものの、特に電力・面積的な制約の大きなエッジ機器で利用する場合に、要求される計算量とメモリ容量の肥大化が問題となっている。これに対処するため、アルゴリズム面から提案されてきたのが、CNNの枝刈り(プルーニング)に代表される、CNNモデルの冗長性を利用し、認識精度を保ったままモデル規模を縮小(スパース化)する手法である。しかしスパース化では、計算量とメモリ容量の削減はできるものの、メモリへのアクセスが不規則になり、データ再利用性と演算器の稼働率が低下し、並列処理の計算効率が低下することが課題になっていた。

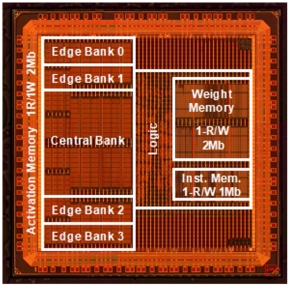

台湾TSMCの40nmプロセスで試作チップを製作

今回の開発成果は、NEDOの「高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発」の下で、東京工業大学(東工大)科学技術創成研究院 教授の本村真人氏らのチームが進めてきたものだ。同チームは、深く枝刈りされたことでメモリへのアクセスが不規則になったCNNの推論処理では、チャネル間の畳み込みと入力データのチャネル内平面シフトを利用して畳み込みの積和演算を行うことが効率的であることを見いだし、そのため並列演算アレイとデータ整形機構を中核としたアーキテクチャを提案した。

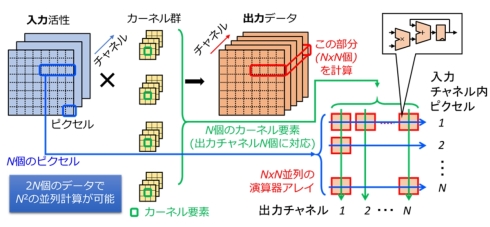

研究開発でまず検討したのは、CNNによる並列演算の計算効率の改善である。CNNの畳み込み層における畳み込み演算は、複数チャネルからなる入力活性とカーネル群から複数チャネルの出力データを生成する積和演算の繰り返しから成っている。互いに依存関係のない入力チャネル内のピクセル位置と出力チャネル方向の座標軸を選ぶと、積和演算を各行・各列で独立の積(直積)と和の計算に分離でき、データ再利用性を高く保つ並列計算が可能になり、計算効率が高くなる。この方式は、カーネルサイズ1×1のチャネル間畳み込み(いわゆるPoint-wise畳み込み※))において、特に計算効率が高くなる。

※)Point-wise畳み込み:畳み込みのうち、カーネル係数のXYサイズが1×1であり、チャネル間の畳み込みのみを担当するものは特にPoint-wise畳み込みと呼ばれる。入力活性のXY平面のピクセル間の相関を考慮しないで、チャネル方向(特徴空間)の変換のみを担う。これとは対照的に、チャネル方向を考慮しないで、チャネル内でのピクセルの変換のみを扱う畳み込みはDepth-wise畳み込みと呼ばれる。通常の畳み込みをDepth-wise畳み込みとPoint-wise畳み込みのペアで近似することで、必要メモリ容量の削減を図ったCNNモデルとして、これまでにMobileNetが提案されている。

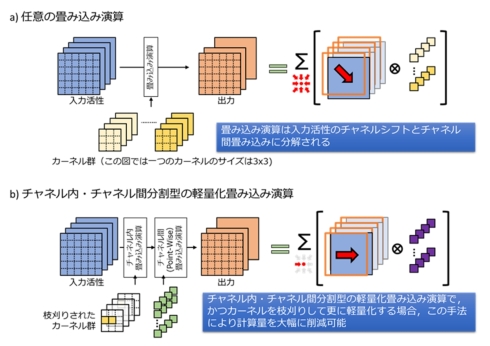

次に、計算効率のアルゴリズムの改善を検討した。ここで着目したのが、一般にあらゆる畳み込み演算が入力データのチャネル内平面シフトとカーネルサイズ1×1のチャネル間(Point-wise)畳み込みの組み合わせに分解できることだ。特に、チャネル内とチャネル間にカーネルを分離することで軽量化された畳み込み演算に対しては、入力データのチャネル内平面シフトを扱う整形機構によりチャネル内の畳み込み演算を処理し、直積型並列演算器アレイによりチャネル間の畳み込み演算を処理することで、高いデータ再利用率で処理できることを見いだした。さらに、畳み込みカーネルをカーネル要素の座標に合わせて枝刈りすると、存在しないカーネル要素に対応する計算をスキップでき、メモリアクセス・演算処理を省ける。これにより、深く枝刈りされたCNNの計算効率をより向上させることができた。

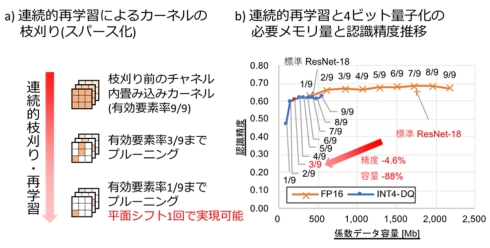

続いて、既存のCNNモデルを変形し、同一座標のカーネル要素を優先して枝刈りする学習アルゴリズムを構築した。モデルの処理時間・効率と認識精度は、枝刈り後に残存するカーネル要素数(スパース率の逆数)によってトレードオフの関係となる。開発したアルゴリズムは、既存の学習済みモデルに対して連続的にカーネル要素数を減らしながら再学習を行うもので、求める処理時間・効率と認識精度から、スパース率のトレードオフ点を任意に選択することが可能になった。

これらの研究に基づくアーキテクチャの試作チップを台湾TSMCの40nmプロセスで製作した。並列演算アレイサイズを32×32とし、活性値・係数値には4ビット固定小数点(INT4)量子化を採用した。その結果、最大動作周波数534MHz/動作電圧1.1Vの条件で400mW以内の電力消費を実測した。これは、カーネル要素数を9分の1まで枝刈りした後のスパース化した不要カーネル要素の省略を考慮すると、スマートフォンなどのエッジ機器向けCNN推論プロセッサとして世界トップレベルの実効効率となる、消費電力1W当たり26.5TOPSに相当するという。

なおこれらの開発成果は、2021年8月22〜24日にオンラインで開催されているプロセッサLSIの主要国際会議である「Hot Chips 33」に採択され、東京工業大学がポスターセッションで発表する予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

エッジAIの可能性を広げる「MST」、なぜCortex-M0+マイコンでも動くのか

エッジAIの可能性を広げる「MST」、なぜCortex-M0+マイコンでも動くのか

エッジAIスタートアップのエイシングは、マイコンを使って、AIによる推論実行だけでなく学習も行えるアルゴリズム「MST」を開発した。ローエンドの「Cortex-M0+」を搭載するマイコンでも動作するMSTだが、より多くのメモリ容量が求められるランダムフォレストと同等の精度が得られるという。開発の背景を同社 社長の出澤純一氏に聞いた。 「Jetson Xavier NX」で組み込みAIを試す

「Jetson Xavier NX」で組み込みAIを試す

2020年5月14日に行われたNVIDIAの「GTC 2020」の基調講演で発売がアナウンスされた、組み込みAIボード「Jetsonシリーズ」の最新製品となる「Jetson Xavier NX」。「Jetson Nano」の連載を担当した技術ライターの大原雄介氏に、Jetson Xavier NXの開発者キットをレビューしてもらった。 学習済みAIを多様なエッジに展開する「スケーラブルAI」、東芝と理研が新技術

学習済みAIを多様なエッジに展開する「スケーラブルAI」、東芝と理研が新技術

東芝と理化学研究所が学習済みのAIについて、演算量が異なるさまざまなシステムへの展開を可能にする「スケーラブルAI」の新技術を開発。従来技術と比べてAI性能の低下率を大幅に抑制し「世界トップレベル」を実現したという。 ザイリンクスがエッジAI向け新製品、単位ワット当たりの性能は「NVIDIAの4倍」

ザイリンクスがエッジAI向け新製品、単位ワット当たりの性能は「NVIDIAの4倍」

ザイリンクスは2021年6月9日(現地時間)、7nmプロセスを採用した適応型演算プラットフォーム「Versal ACAP(Adaptive Compute Acceleration Platform)」に自動運転車や協働ロボットなどエッジ向けの新シリーズ「Versal AIエッジ ACAP」を追加したと発表した。 デバイスへの最適化を自動実行、エッジAIアプリの開発を10倍高速化する開発基盤

デバイスへの最適化を自動実行、エッジAIアプリの開発を10倍高速化する開発基盤

フィックスターズは2021年1月22日、カメラなどに搭載するエッジAIアプリケーション開発プラットフォーム「GENESIS DevEnv」の製品版を公開すると発表した。CPUやGPUなど各種デバイスを手元にそろえることなく、コードの自動最適化が行える。この他、エッジAIアプリ開発のひな型となるテンプレートの活用などで、開発工程の自動化や省力化を実現する。 Jetson Nanoで組み込みAIを試す

Jetson Nanoで組み込みAIを試す

MONOistやEE Times Japanに掲載した主要な記事を、読みやすいPDF形式の電子ブックレットに再編集した「エンジニア電子ブックレット」。今回は、NVIDIAの組み込みAIボード「Jetson Nano」の立ち上げから、一般的な組み込みAIとしての活用までを含めていろいろと試した連載「Jetson Nanoで組み込みAIを試す」をまとめた。