世界初のマイクロプロセッサ「4004」から50年、今やトランジスタ数は100万倍に:組み込み開発ニュース(2/2 ページ)

インテルは、オンラインで会見を開き、世界初のマイクロプロセッサとして知られる同社の「4004」が発表から50周年を迎えたことと併せて、最新技術となる第12世代「Core」プロセッサファミリーについて紹介した。

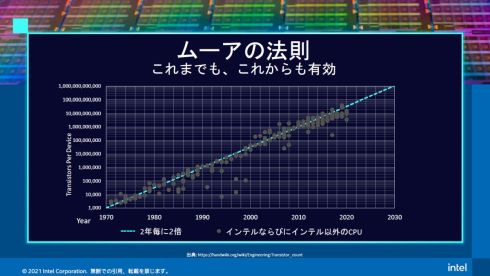

「これまでも、これからも、ムーアの法則は有効」

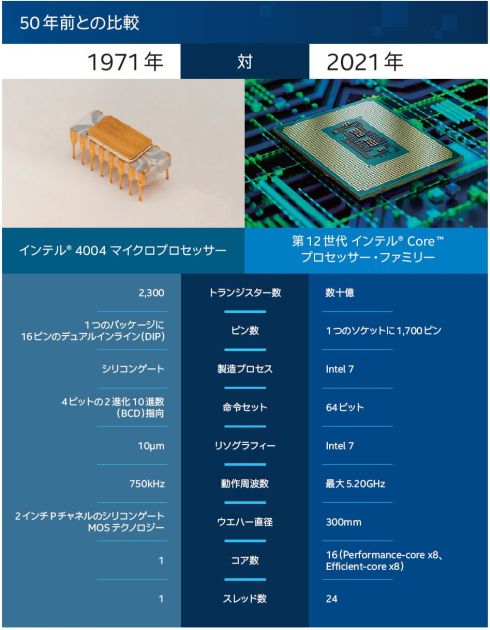

インテルの最新製品は、コードネーム「Alder Lake」に当たる第12世代Coreプロセッサファミリーになる。50年前に発表された4004と比較すると、製造プロセスは10μmから10nm(Intel 7)となり、トランジスタ数は2300から数十億と100万倍に達している。端子数は16ピンから1700ピン、命令セットも4ビットから64ビットとなり、動作周波数は750kHzから最大5.2GHzまで向上している。50年間におけるこれらの大きな進化は、インテル創業者の一人であるゴードン・ムーア(Gordon Moore)氏が提唱した「ムーアの法則」に基づくものだ。

ムーア氏は1965年に、今後10年間は集積回路の複雑性が毎年約2倍の比率で増大すると発表し、その10年が経過した1975年には、今後10年間は2年ごとに2倍の比率で増大すると予測している。これがムーアの法則である。2年ごとに2倍のペースは現在も維持されており「微細化が難しくなっていることから限界もささやかれているが、インテルはこれまでも、これからも、ムーアの法則は有効だと考えている」(土岐氏)。

現在リリースされている第12世代Coreプロセッサは、オーバークロックに対応するデスクトップ向け製品になる。ゲーミングとコンテンツ制作で高い性能を発揮し、競合となるAMDの「Ryzen 5950X」よりも高い処理性能を実現できている。

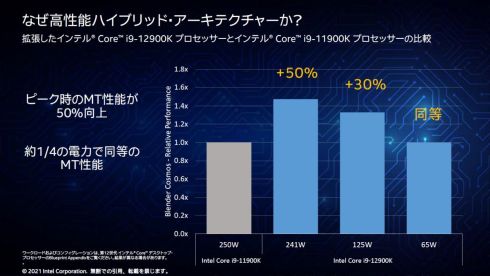

また、Alder Lakeでは高性能の「Performance Core」と高効率の「Efficient Core」を組み合わせたハイブリッドアーキテクチャを特徴としている。前世代の第11世代Coreと比べて、Performance Coreを用いるピーク時性能は同じ消費電力でも50%向上し、Efficient Coreを用いる場合には同じ性能を約4分の1の消費電力で実現できるとしている。

Alder Lakeで導入された「スレッド・ディレクター」をアプリケーション側で活用すれば、さらに処理性能を向上できるとしている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

CPU・MPUはどうやって動く?

CPU・MPUはどうやって動く?

CPU(MPU)の基礎知識をおさらいする。重要なのは「どこから命令を持ってくるか」と「どこに実行結果を書き込むか」の2点だ インテルが半導体プロセスノードを再定義、2024年にはオングストローム世代へ

インテルが半導体プロセスノードを再定義、2024年にはオングストローム世代へ

インテル日本法人が、米国本社が2021年7月26日(現地時間)にオンライン配信したWebキャスト「Intel Accelerated」で発表した先端半導体製造プロセスやパッケージング技術について説明した。 インテルの最新CPUアーキテクチャはより広く深く、GPUがHPCのムーンショットに

インテルの最新CPUアーキテクチャはより広く深く、GPUがHPCのムーンショットに

インテル日本法人は、米国本社が2021年8月19日(現地時間)に開催したイベント「Intel Architecture Day 2021」で発表した、新たなCPUとGPUのアーキテクチャについて説明した。 10nm採用の第3世代「Xeon SP」はエッジでも展開、AI性能はNVIDIA「A100」の1.3倍

10nm採用の第3世代「Xeon SP」はエッジでも展開、AI性能はNVIDIA「A100」の1.3倍

インテル日本法人がデータセンター向けの「Xeonスケーラブル・プロセッサー(以下、Xeon SP)」の第3世代品を発表。10nmプロセスを採用することで、14nmプロセスの第2世代Xeon SPと比べて平均46%の性能向上を果たした。主な用途は、クラウド、エンタープライズ、HPC、5Gの他、IoTなどエッジでの利用も可能としている。 新CEOの「IDM 2.0」がインテルを戒めから解き放つ、ファウンドリー事業にも本腰

新CEOの「IDM 2.0」がインテルを戒めから解き放つ、ファウンドリー事業にも本腰

インテルが、7nmプロセスの進捗状況や、ファウンドリー事業の立ち上げ、工場の建設計画などについて発表。2021年2月に新CEOに就任したパット・ゲルシンガー氏がグローバルWebキャストに登壇し、同社がこれまで堅持してきたIDM(垂直統合型デバイス製造)を大きく進化させる「IDM 2.0」のビジョンについて説明した。 2nm以降世代に向けた半導体プロジェクトが始動、かつての国プロとの違いとは

2nm以降世代に向けた半導体プロジェクトが始動、かつての国プロとの違いとは

NEDOと経済産業省、AIST、TIAの4者が「先端半導体製造技術つくば拠点オープニングシンポジウム」を開催。「ポスト5G情報通信システム基盤強化研究開発事業」の中で進められる「先端半導体製造技術の開発」のキックオフに当たるイベントで、2nm世代以降のロジックICを対象とした前工程プロジェクトと、3D ICを対象とした後工程プロジェクトについての説明が行われた。