ルネサスが新たなエッジAI技術を開発、世界最高クラスの電力効率と推論精度:人工知能ニュース(2/4 ページ)

ルネサス エレクトロニクスは2019年6月13日、低消費電力で高速にCNN(畳み込みニューラルネットワーク)の推論を実行できるAI(人工知能)アクセラレータ技術を開発したと発表した。同技術を用いたテストチップは高い推論精度を維持しつつ、世界最高クラス(同社調べ)となる8.8TOPS/Wの電力効率を実現した。

Ternary SRAMのPIMで演算精度を確保

同社が開発した技術もSRAMを用いたPIMとなるが、既報と比較して「−1・0・1」の3値(Ternary)を保存するSRAM構造へのPIM実装、コンパレーターによるメモリデータ読み出しの低消費電力化、製造プロセスのばらつきによる演算誤差の回避、の3点に特徴がある。それぞれ詳細を紹介したい。

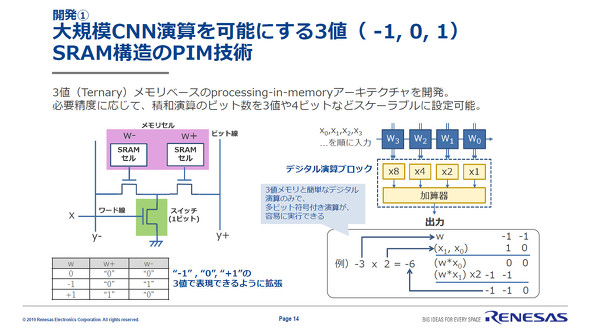

1点目のTernary SRAM構造へのPIM実装は、現在広く用いられている(Binaryな)SRAMからメモリセルの構造を拡張し、デジタル演算ブロックを追加したものとなる。今回用いたTernary SRAM構造は、ワード線(下図のX)とビット線対(Y−、Y+)をつなぐMOSFETが3個あり、ビット線対に直結する2個のMOSFETにそれぞれメモリセル(W−、W+)がひも付いている。

これら2個のメモリセルは「どちらもゼロ」「一方がゼロ、一方が1(逆もカウントする)」の3通りの状態を取る。この状態それぞれを「−1・0・1」と定義することで、3値(1.5ビット)のウェイトを保存できるSRAM構造とした。なお、メモリセルが「どちらも1」となる状態はビット線がショートするため定義していない。このSRAM構造とビットシリアル演算ブロックを組み合わせることで、多ビット符号付き演算も容易に実行可能だ。

同方式について、ルネサスの担当者は「ウェイトの情報量が増えるのでニューラルネットワークの推論精度も改善する。また、どちらのビット線にも電流を流さないケースもあるので低消費電力だ。推論精度を上げたいときに4ビットまで演算精度を増やすことができ、ビットスケーラビリティが高い」とメリットを説明する。

コンパレーターでメモリデータ読み出し、演算結果ゼロでは動作停止も

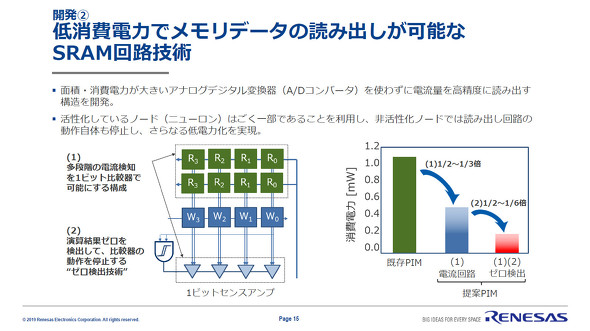

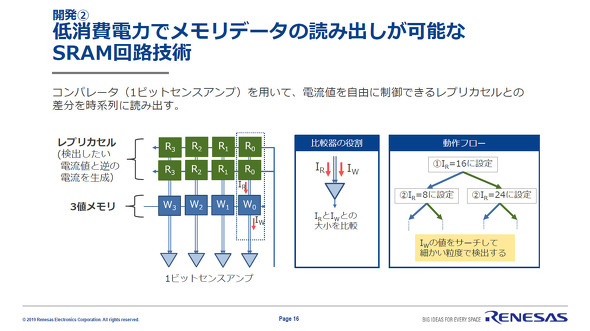

PIMではメモリデータの読み出し精度が演算処理の精度に影響するため、高精度なビット線電流の測定が求められる。この場合、A-Dコンバーターを用いることが有効だが、高い消費電力とチップ面積の増加が課題となる。新開発の技術ではA-Dコンバーターを用いず、1ビットセンスアンプとレプリカセルを組み合わせることで高精度な電流量計測を可能とした。

レプリカセルはメモリセル内にSRAMセルがない単なる電流源となっており、複数のレプリカセルにより多段階の電流を任意に流すことができる。1ビットセンスアンプはビット線電流とレプリカセル由来の電流を比較するコンパレーターとしての機能を持ち、二分探索木によってビット線電流値とレプリカセル由来の電流値を判定する。これにより、A-Dコンバーターを用いた既存のPIM技術と比べて2分の1〜3分の1の消費電流で動作が可能とする。

また、ニューラルネットワークは発火(電気信号の閾値がある一定の量を超えること)しているが全体の1%程度とごく一部で、発火しないニューロンはゼロを出力するという特性を生かし、発火しないニューロンでは読み出し回路の動作を停止する技術も実装。上述したメモリデータ読み出し技術の改善から、さらに2分の1〜6分の1の低電力化を実現した。

Copyright © ITmedia, Inc. All Rights Reserved.