名刺大FPGA開発ボード「Ultra96」は3万円、推論アルゴリズムの実装も容易に:ESEC2019&IoT/M2M展

アヴネットは、「第8回 IoT/M2M展 春」において、名刺サイズのFPGA開発プラットフォーム「Ultra96」を用いた画像認識デモを披露した。

アヴネットは、「第8回 IoT/M2M展 春」(2019年4月10〜12日、東京ビッグサイト)において、名刺サイズのFPGA開発プラットフォーム「Ultra96」を用いた画像認識デモを披露した。

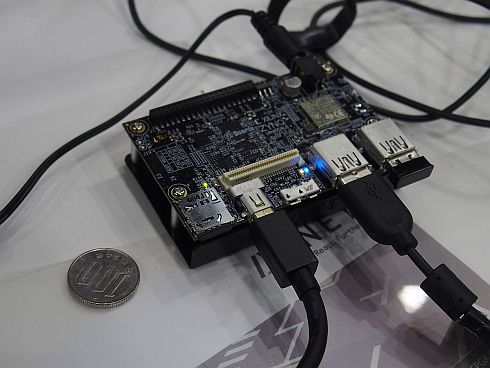

Ultra96は、ザイリンクスのプログラマブルSoC「Zynq UltraScale+ MPSoC(以下、MPSoC)」を搭載する開発ボードだ。Linaroが提唱する「96Boards Consumer Edition」仕様に準拠しており、外形寸法は85×54mmで、Wi-FiやBluetoothなどの通信機能、USBやMini DisplayPortなどのインタフェース、2GBのLPDDR4メモリなどを備えている。高価な最先端のプログラマブルSoCであるMPSoCを搭載しながら、販売価格は「破格の」(アヴネットの説明員)3万円を実現している(搭載するMPSoCの品種は「ZU3EG」)。

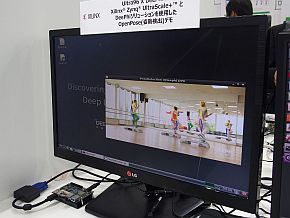

デモでは、ザイリンクスが2018年7月に買収したDeePhi Techの深層学習(ディープニューラルネットワーク)開発キット「DEEPHi DNNDK」を用いて、顔認識や姿勢検出の推論アルゴリズムをUltra96のMPSoCに実装。来場者の顔認識などを行っていた。「MPSoCのFPGA回路を活用することで、CPUだけを使うのと比べて約10倍の処理性能を実現している。顔認識であれば十数fpsくらい出ているだろう」(同説明員)。

Ultra96と同様の小型開発ボードでは、2019年3月にNVIDIAが販売価格99米ドルで発表した「Jetson Nano」などがある。「エッジで推論アルゴリズムを動かす場合、実用的には浮動小数点ではなく固定小数点で演算処理することになるだろう。その場合MPSoCは、高い処理性能だけでなく消費電力も抑えられる点で実用的だ。また、FPGAへの推論アルゴリズム実装が難しいという話もよく聞くが、今回使ったDEEPHi DNNDKはとても使いやすいので試してほしい」(同説明員)としている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

組み込みAIは必要不可欠な技術へ、推論に加えて学習も視野に

組み込みAIは必要不可欠な技術へ、推論に加えて学習も視野に

2017年初時点では芽吹きつつあった程度の組み込みAI。今や大きな幹にまで成長しつつあり、2019年からは、組み込み機器を開発する上で組み込みAIは当たり前の存在になっていきそうだ。 ラズパイゼロで推論も学習もできる組み込みAI「DBT」、“AIチップ”で開発容易に

ラズパイゼロで推論も学習もできる組み込みAI「DBT」、“AIチップ”で開発容易に

AIベンチャーのエイシングが、組み込み機器などのプロセッサでAIの推論実行だけでなく学習も行える独自技術「DBT」について説明。このDBTによるアプリケーション開発を容易に行えるAIモジュール「AiiR(エアー)チップ」を開発したと発表した。 ET展で組み込みAIはなぜ盛り上がらないのか

ET展で組み込みAIはなぜ盛り上がらないのか

2016年、2017年に引き続き、エレクトロニクス/組み込み分野に詳しい大原雄介氏による「ET2018/IoT Technology 2018」の“獣道”レポートをお送りする。中国発の注目のArmチップや新たなLPWA規格などの展示があったものの、組み込みAI関連の展示は盛り上がらなかったようで……。 中高生向けの自動運転車の開発、99ドルのボードで「AIの可能性を知って」

中高生向けの自動運転車の開発、99ドルのボードで「AIの可能性を知って」

NVIDIAがユーザーイベント「GTC 2019」(2019年3月19〜21日、米国カリフォルニア州サンノゼ)で発売を発表した組み込みAI(人工知能)の開発者キット「Jetson NANO」。使い道にひときわ関心を寄せたのは、子どもを持つGTC参加者たちだ。 百度のエッジAIアプリケーションが「Zynq UltraScale+ MPSoC」を採用

百度のエッジAIアプリケーションが「Zynq UltraScale+ MPSoC」を採用

Xilinxは、Baidu(百度)製のエッジAIアプリケーション「EdgeBoard」に、「Zynq UltraScale+ MPSoC」が採用さ 画像認識の機械学習アルゴリズムを容易に組み込める、ザイリンクスが新開発環境

画像認識の機械学習アルゴリズムを容易に組み込める、ザイリンクスが新開発環境

ザイリンクスは、機械学習ベースの画像認識アルゴリズムを組み込み機器で容易に活用するための開発環境「reVISIONスタック」を発表した。2017年4〜6月期の市場投入する計画。