FPGAソフトコアCPUにおける最適化を検証する:MAX 10 FPGAで学ぶFPGA開発入門(14)(1/7 ページ)

MAX10搭載開発ボード「MAX 10 NEEK」でソフトコアCPU「NIOS II」を利用する際、最適化しないことを推奨されるが、設定自体は施せる。では最適化すると速くなるのか?有償版も含めて検証する。

アルテラのFPGA「MAX 10」を用いた開発手法を紹介しているこの連載も、今回でいったんの終了となる。MAX 10 NEEKを手に入れてから、FPGAというよりはソフトコアCPUである「NIOS II」にターゲットがシフトした感もあるのだが、最終回も引き続きNIOS IIの性能をもうちょっと追いかけてみたいと思う。

以前にも触れたが、NIOS IIを使う場合には最適化を行わないよう指示されている。プログラム実行に問題の生じる可能性があるためとされているが、最適化しなければ性能が出ないのもまた当然である。そこで、ベンチマークプログラムを用意して最適化の効果を検証したい。

System Builderでの環境構築

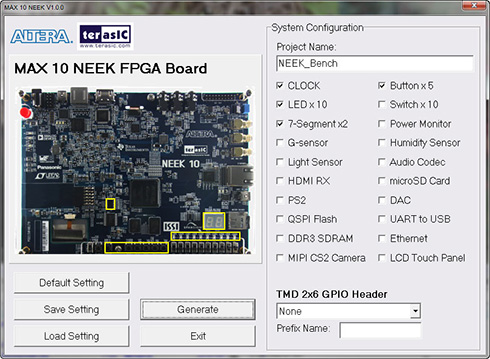

まずはおなじみのSystem Builder(Photo01)でテンプレートを作る。今回は(あまり使う意味はないのだが)7セグメントLEDと10個のLED、プッシュボタン(とClock)を有効にした。プロジェクト名は「NEEK_Bench」としたので、CodeGenerate/MAX10/ の下に「NEEK_Bench」というフォルダが生成される。これを丸ごとQuartus IIのプロジェクトディレクトにコピーする。

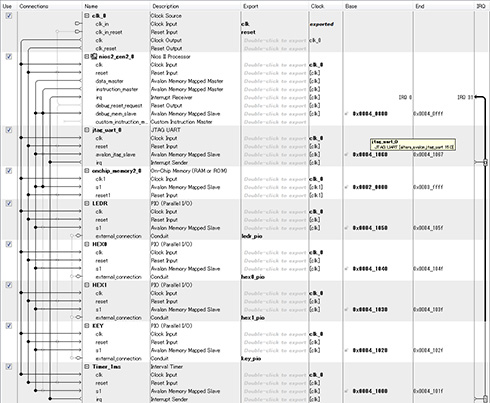

次にQuartus II(15.0を利用)を起動して、“File” → “Open Project...”で“NEEK_Bench.qpf”を選択する。初期状態ではNEEK_Bench.vの中にはNEEK_Benchというモジュール定義が行われているだけなので、ここからqsysを動かして、コンポーネントを追加する。追加するのはプロセッサコア、JTAG UART、オンチップメモリ、LEDR、HEX0、HEX1、KEY、タイマーの8つだ。

| コンポーネント | 追加方法 |

|---|---|

| プロセッサコア | "Processors and Peripherals" → "Embedded Processors" → "NIOS II Processor"で追加。種別はNIOS II/eを指定 |

| JTAG UART | "Interface Protocols" → "Serial" → "JTAG UART" |

| オンチップメモリ | "Basic Functions" → "On Chip Memory" → "On-Chip Memory (RAM or ROM)"。メモリ容量は128KBとし、"Initialize memory content"のチェックを外しておく。またこれを追加後に、nios2_gen2_0のプロパティを開き、"Vectors"タブで"Reset Vector"と"Exception Vector"を共に"onchip_memory2_0.s1"に設定する。 |

| LEDR(LED×10) | "Processors and Peripherals" → "Peripherals" → "PIO(Parallel I/O)"でPIOを追加する。この際Widthを10bit、DirectionはOutputを指定し(Photo02)、名前を"LEDR"に変更する。またConduitを"ledr_pio"とする。 |

| HEX0(7セグメントLED #1) | "Processors and Peripherals" → "Peripherals" → "PIO(Parallel I/O)"でPIOを追加する。この際Widthを7bit、DirectionはOutputを指定し、名前を"HEX0"に変更する。またConduitを"hex0_pio"とする。 |

| HEX1(7セグメントLED #2) | "Processors and Peripherals" → "Peripherals" → "PIO(Parallel I/O)"でPIOを追加する。この際Widthを7bit、DirectionはOutputを指定し、名前を"HEX1"に変更する。またConduitを"hex1_pio"とする。 |

| KEY(Button×5) | "Processors and Peripherals" → "Peripherals" → "PIO(Parallel I/O)"でPIOを追加する。この際Widthを5bit、DirectionはInputを指定し、名前を"KEY"に変更する。またConduitを"key_pio"とする。 |

| タイマー | "Processors and Peripherals" → "Peripherals" → "Interval Timer"で追加。Periodは1msを指定。Counter Sizeは32bitのままとすし、名前を"Timer_1ms"とする。 |

追加後に各コンポーネントの結線を行い(Photo02)、さらにQsysの“System” → “Assign Base Address”でアドレスの割り当て直しを行う。これで基本的にQsysのエラーが消えるはずなので、“NEEK_BENCH_QSYS”という名前をつけて保存した上で、“Generate HDL”を押してqipファイルを生成しQsys側の作業は終了である。

ついでNEEK_Bench.vの編集である。こちらも従来とあまり変わらず、最終的にList 1の様に、「NEEK_BENCH_QSYS」というモジュールを呼び出す設定だけを追加すれば完了である。

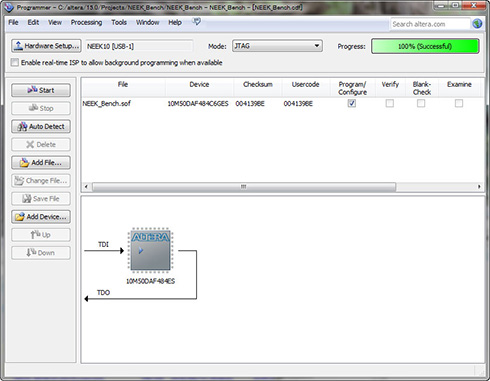

これが終わったらコンパイルし、エラーがなければProgrammerでNEEK_Bench.sofを書き込んでQuartus II側の作業は終了である(Photo03)。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

FPGAの内蔵温度センサーから値を得る

FPGAの内蔵温度センサーから値を得る

アルテラのFPGA「MAX 10」には温度センサーが内蔵されており、自身の温度を測定可能だ。メガファンクション「ALTPLL」を使い、内蔵センサーからの値を得るまでを試みる。 オンボードされた温湿度センサーからFPGAで値を得る

オンボードされた温湿度センサーからFPGAで値を得る

FPGA「MAX 10」搭載開発ボード「MAX 10 NEEK」には各周辺機器が備えられており、そこにはTI製の温湿度センサーも含まれる。サンプルプログラムを元に、オンボードされたデバイスの制御を試みる。 「MAX 10 NEEK」でストップウォッチを開発し、内蔵メモリから起動する

「MAX 10 NEEK」でストップウォッチを開発し、内蔵メモリから起動する

アルテラのFPGA「MAX 10」を搭載した開発ボード「MAX 10 NEEK」にはLEDやフラッシュメモリなどの各周辺機器が備えられている。今回はLEDを使ったストップウォッチを開発し、内蔵メモリから起動する。 「MAX 10 NEEK」に搭載されたDDR3メモリを使う

「MAX 10 NEEK」に搭載されたDDR3メモリを使う

MAX10搭載開発ボード「MAX 10 NEEK」には各周辺機器が備えられており、その中にはDDR3メモリも含まれる。ソフトコアCPU「Nios II」からの利用も含めて手順を紹介する。 「MAX 10 NEEK」へソフトコアCPUを組み込む

「MAX 10 NEEK」へソフトコアCPUを組み込む

周辺機器の充実したMAX10搭載開発ボード「MAX 10 NEEK」に、ソフトコアCPU「NIOS II」を組み込み、ソフトコアCPUからボード搭載LEDの制御までを紹介する。