「MAX 10 NEEK」でストップウォッチを開発し、内蔵メモリから起動する:MAX 10 FPGAで学ぶFPGA開発入門(11)(1/10 ページ)

アルテラのFPGA「MAX 10」を搭載した開発ボード「MAX 10 NEEK」にはLEDやフラッシュメモリなどの各周辺機器が備えられている。今回はLEDを使ったストップウォッチを開発し、内蔵メモリから起動する。

この連載ではアルテラのFPGA「MAX 10」を題材にしているおり、ここ数回は各種周辺機器も備えたMAX10搭載開発ボード「MAX 10 NEEK」を使って周辺機器へのアクセス方法などを紹介している。

前回(「MAX 10 NEEK」に搭載されたDDR3メモリを使う)はDDR3を利用する方法を説明したが、今回は内蔵Flashを使ってみたい。

もともとMAX 10の場合、内部にFlash Memoryを保持しており、ブート時にはここからConfigurationを読み出して即座に実行できるので、これを利用できるようにしてみたい。もちろん、ソフトコアCPUの「NIOS II」を含めて、である。

下準備

さてまずは前準備。今回は連載 第9回(「MAX 10 NEEK」へソフトコアCPUを組み込む)で紹介した内容をもとに簡単なストップウォッチをNIOS IIベースで構築してみる。

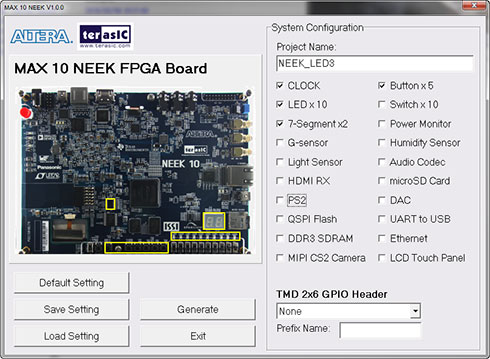

第9回ではNOIS IIの組み込みがメインであったので、LEDと7セグメントLEDはを組み込んだだけ(しかも実際には使わなかった)だったが、今回はこれを活用する。ついでにボタン×5(実際はうち4つ)も活用する。ということで、最初はSystem Builderである(Photo01)。プロジェクト名はひねりがなくて恐縮だが「NEEK_LED3」だ。

ファイルが生成されたら、それをQuartus II(今回も15.0を使った)のプロジェクトディレクトリにコピーしたのち、Quartus IIでそのプロジェクトを開く。次いでQSYSを立ち上げて、プロセッサコアとJTAG UART、オンチップメモリを組み込む手順までは第9回と同様だが、追加で作業を行う。

| 対象 | 手順 |

|---|---|

| プロセッサコア | "Processors and Peripherals" → "Embedded Processors" → "NIOS II Processor" |

| JTAG UART | "Interface Protocols" → "Serial" → "JTAG UART" |

| オンチップメモリ | "Basic Functions" → "On Chip Memory" → "On-Chip Memory (RAM or ROM)"(メモリは128KBにした) |

| 対象 | 手順 |

|---|---|

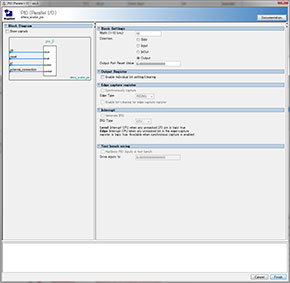

| LEDR(LED×10) | "Processors and Peripherals" → "Peripherals" → "PIO(Parallel I/O)"でPIOを追加する。この際Widthを10bit、DirectionはOutputを指定し(Photo02)、追加後に名前を"LEDR"に変更する。 |

| HEX0(7セグメントLED #1) | "Processors and Peripherals" → "Peripherals" → "PIO(Parallel I/O)"でPIOを追加する。この際Widthを7bit、DirectionはOutputを指定し、追加後に名前を"HEX0"に変更する。 |

| HEX1(7セグメントLED #2) | "Processors and Peripherals" → "Peripherals" → "PIO(Parallel I/O)"でPIOを追加する。この際Widthを7bit、DirectionはOutputを指定し、追加後に名前を"HEX1"に変更する。 |

| KEY(Button×5) | "Processors and Peripherals" → "Peripherals" → "PIO(Parallel I/O)"でPIOを追加する。この際Widthを5bit、DirectionはInputを指定(Photo03)、追加後に名前を"KEY"に変更する。 |

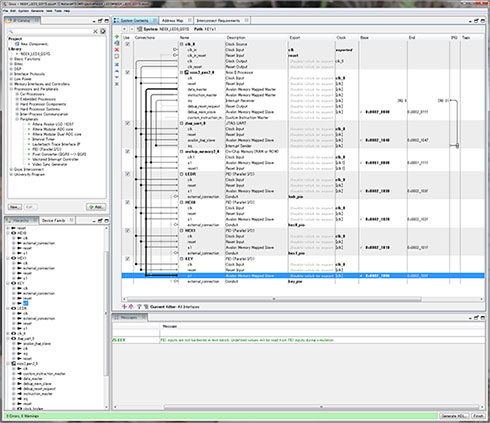

これらの手順を終えると、最終的にはこんな感じになる(Photo04)。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「MAX 10 NEEK」に搭載されたDDR3メモリを使う

「MAX 10 NEEK」に搭載されたDDR3メモリを使う

MAX10搭載開発ボード「MAX 10 NEEK」には各周辺機器が備えられており、その中にはDDR3メモリも含まれる。ソフトコアCPU「Nios II」からの利用も含めて手順を紹介する。 「MAX 10 NEEK」へソフトコアCPUを組み込む

「MAX 10 NEEK」へソフトコアCPUを組み込む

周辺機器の充実したMAX10搭載開発ボード「MAX 10 NEEK」に、ソフトコアCPU「NIOS II」を組み込み、ソフトコアCPUからボード搭載LEDの制御までを紹介する。 周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

FPGA開発において周辺機器(回路)は見落とせない要素の1つ。タッチパネルや各種出入力などを備えた「MAX 10 NEEK」を導入して、本格的な開発を目指す。 FPGAのソフトコアCPUをベンチマークで測定する

FPGAのソフトコアCPUをベンチマークで測定する

FPGA「MAX10」に「NIOS II」と呼ばれるソフトIPコアを導入することで、ソフトコアCPUを構築できる。ではその処理能力はどれほどか。ベンチマークソフトで測定してみよう。 FPGA上でソフトコアCPUを動かす手引き

FPGA上でソフトコアCPUを動かす手引き

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。