連載

「MAX 10 NEEK」に搭載されたDDR3メモリを使う:MAX 10 FPGAで学ぶFPGA開発入門(10)(3/6 ページ)

MAX10搭載開発ボード「MAX 10 NEEK」には各周辺機器が備えられており、その中にはDDR3メモリも含まれる。ソフトコアCPU「Nios II」からの利用も含めて手順を紹介する。

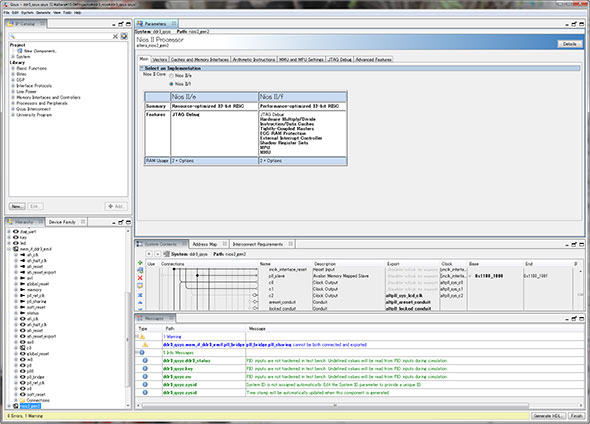

以下Photo08〜Photo13が、そのDDR3 I/Fまわりのパラメータとなる。今回はこれをいじる必要はないが、自分でDDR3を利用して何かやりたい、という場合にはこれに準じる形でパラメータの設定を行う事になる。また今回、デフォルトではCPUコアはNios II/fとなっている(Photo14)。これはTerasicがNios II/fのライセンスを保有しており、これを利用して開発を行った為だろう。これについては後でちょっといじって遊ぶが、取りあえずはこのままで行くことにしたい。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「MAX 10 NEEK」へソフトコアCPUを組み込む

「MAX 10 NEEK」へソフトコアCPUを組み込む

周辺機器の充実したMAX10搭載開発ボード「MAX 10 NEEK」に、ソフトコアCPU「NIOS II」を組み込み、ソフトコアCPUからボード搭載LEDの制御までを紹介する。 周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

FPGA開発において周辺機器(回路)は見落とせない要素の1つ。タッチパネルや各種出入力などを備えた「MAX 10 NEEK」を導入して、本格的な開発を目指す。 FPGAのソフトコアCPUをベンチマークで測定する

FPGAのソフトコアCPUをベンチマークで測定する

FPGA「MAX10」に「NIOS II」と呼ばれるソフトIPコアを導入することで、ソフトコアCPUを構築できる。ではその処理能力はどれほどか。ベンチマークソフトで測定してみよう。 FPGA上でソフトコアCPUを動かす手引き

FPGA上でソフトコアCPUを動かす手引き

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

単純なLチカならばFPGAでもそう難しくない。ただ、ダイナミック点灯やそれに伴うソースの最適化については“ならでは”のポイントが散見される。今回も連載で利用している「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。