「MAX 10 NEEK」へソフトコアCPUを組み込む:MAX 10 FPGAで学ぶFPGA開発入門(9)(4/6 ページ)

周辺機器の充実したMAX10搭載開発ボード「MAX 10 NEEK」に、ソフトコアCPU「NIOS II」を組み込み、ソフトコアCPUからボード搭載LEDの制御までを紹介する。

Quartus IIに戻って

さて、ここからはQuartus IIに戻る。左のFiles画面で、まず現在表示中のNEEK_NIOS2.v、それとQSYSで生成したqipファイル(今回だとNEEK_NIOS2_QSYS/synthesis/NEEK_NIOS2_QSYS.qip)をプロジェクトに追加する(Photo20)。

ここでNEEK_NIOS2_QSYS.vの中身を見ると、こんな宣言になっているハズ(Photo21)なので、この記述にあわせて、NEEK_NIOS2.vをこんな風に書き換える(Photo22)。List 1に書き換えた後のソースを示すが、要するにNEEK_NIOS_QSYSへ制御を移す宣言である。この際にクロックソースは、もともと供給される50MHzのもの(MAX10_CLK1_50)を指定し、PIOポートにはLEDRを指定する。リセットは常時Offということで、1(True)を与えておく形だ。

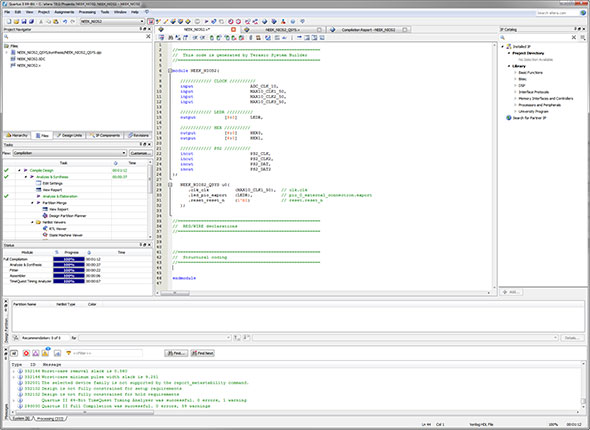

List 1: //======================================================= // This code is generated by Terasic System Builder //======================================================= module NEEK_NIOS2( //////////// CLOCK ////////// input ADC_CLK_10, input MAX10_CLK1_50, input MAX10_CLK2_50, input MAX10_CLK3_50, //////////// LEDR ////////// output [9:0] LEDR, //////////// HEX ////////// output [6:0] HEX0, output [6:0] HEX1, //////////// PS2 ////////// inout PS2_CLK, inout PS2_CLK2, inout PS2_DAT, inout PS2_DAT2 ); NEEK_NIOS2_QSYS u0( .clk_clk (MAX10_CLK1_50), // clk.clk .led_pio_export (LEDR), // pio_0_external_connection.export .reset_reset_n (1'b1) // reset.reset_n ); //======================================================= // REG/WIRE declarations //======================================================= //======================================================= // Structural coding //======================================================= endmodule

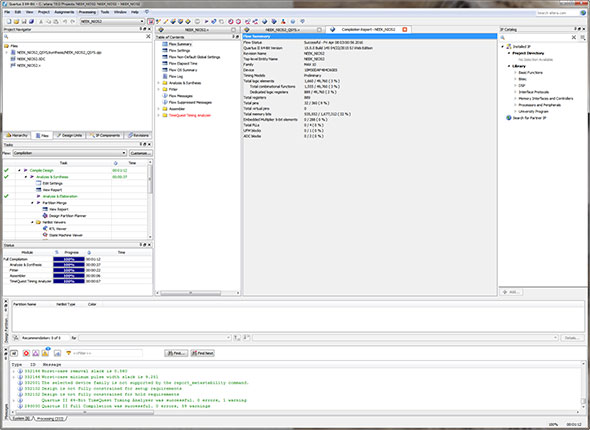

ここまで終わったらVerilog側のプログラミングは完了である。あとはビルドし(Photo23)、問題が無ければProgrammerを利用して.sofファイルを書き込んで置く。

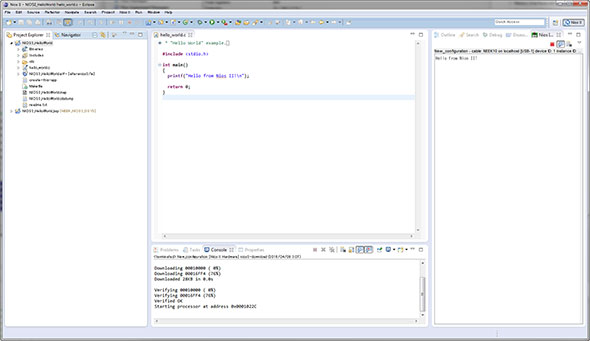

さて、今度はソフトウェアの方だ。Quartus IIから"Tools" → "Nios II Software Build Tools for Eclipse"を選び、Eclipseを立ち上げる。立ち上げたらまず"File" → "New" → "Nios II Application and BSP from Template"を選んでテンプレートから生成する(Photo24)。

今回はメモリもたっぷりあるので、Hello World Smallではなく、Hello Worldを選んでみた。あとは自動でHello WorldとそのBSPが生成されるので、以前と同じ手順でビルドして実行する。問題がなければ、NIOS IIのConsoleに"Hello from Nios II!"が表示されるはずだ(Photo26)。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

FPGA開発において周辺機器(回路)は見落とせない要素の1つ。タッチパネルや各種出入力などを備えた「MAX 10 NEEK」を導入して、本格的な開発を目指す。 FPGAのソフトコアCPUをベンチマークで測定する

FPGAのソフトコアCPUをベンチマークで測定する

FPGA「MAX10」に「NIOS II」と呼ばれるソフトIPコアを導入することで、ソフトコアCPUを構築できる。ではその処理能力はどれほどか。ベンチマークソフトで測定してみよう。 FPGA上でソフトコアCPUを動かす手引き

FPGA上でソフトコアCPUを動かす手引き

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

単純なLチカならばFPGAでもそう難しくない。ただ、ダイナミック点灯やそれに伴うソースの最適化については“ならでは”のポイントが散見される。今回も連載で利用している「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAでのLチカをVerilog HDLで理解する

FPGAでのLチカをVerilog HDLで理解する

今回はFPGAでのLチカを例に、FPGA開発に必要なハードウェア記述言語の解説をしたい。用いる「Verilog HDL」はArduinoやCの経験がある方なら、理解そのものはそう難しくないと思う。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 「MAX 10 FPGA」のテスト環境を構築する

「MAX 10 FPGA」のテスト環境を構築する

今回から実際に「MAX 10 FPGA評価キット」を利用しての開発に着手する。まずは環境構築だ。キット以外に必要なモノもあるので注意して欲しい。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。