「MAX 10 NEEK」へソフトコアCPUを組み込む:MAX 10 FPGAで学ぶFPGA開発入門(9)(2/6 ページ)

周辺機器の充実したMAX10搭載開発ボード「MAX 10 NEEK」に、ソフトコアCPU「NIOS II」を組み込み、ソフトコアCPUからボード搭載LEDの制御までを紹介する。

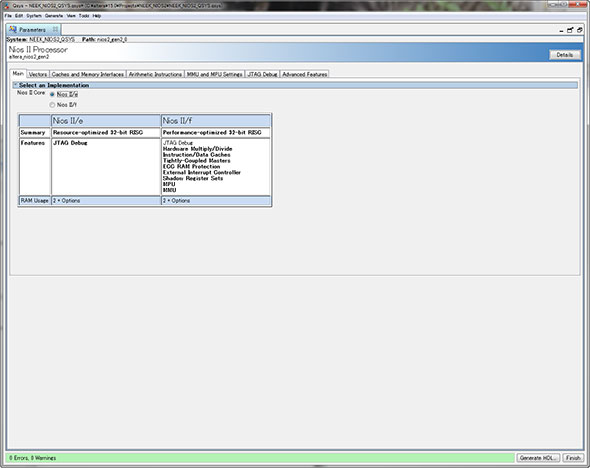

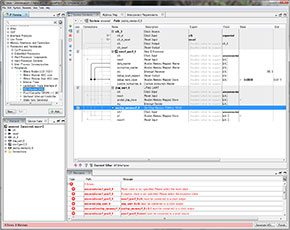

ちなみにMAX 10 NEEKに搭載されている10M50DAF484C6GはLE(Logic Elements)が50K、Block Memoryも1638Kbit(204.75KB)と最大規模のものなので、ついNios II/fを選択したくなるのだが、こちらは有償扱い(一応無償で利用できるOpenCore Plusベースのものが利用できるが、時間制限付き)なので、諦めてNios II/eを選択する(Photo05)。

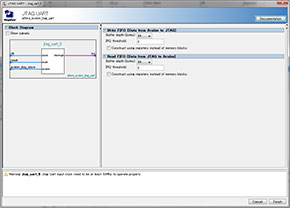

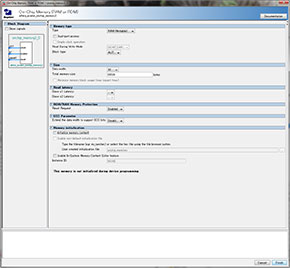

設定画面に戻るとエラーが出ているが(Photo06)、それは気にせずに次は"Interface Protocols" → "Serial" → "JTAG UART"を追加する(Photo07)。その次は、"Basic Functions" → "On Chip Memory" → "On-Chip Memory (RAM or ROM)"でRAMを登録する(Photo08)。

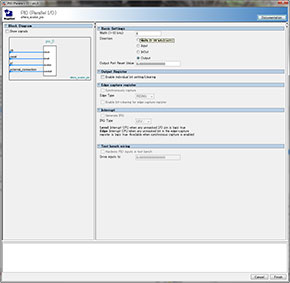

ここで容量は64KBを選んだが、これはまぁこの位あれば取りあえずいいだろうという事であって、デフォルトの4KBのままでも今回の用途には十分である。むしろ注意点は、"Memory Initialization"の所にある"Initialize memory context"のチェックを外しておく事だ(Photo09)。

最後に、10個のLEDの点滅用のParallel I/Oポートの指定である(Photo10)。"Processors and Peripherals" → "Peripherals" → PIO( Parallel I/O )"を指定する形だ。今回はLEDが10個なので、Widthには10を指定する(Photo11)。あと、デバイスの名前を"pio_0"に変更しておく。

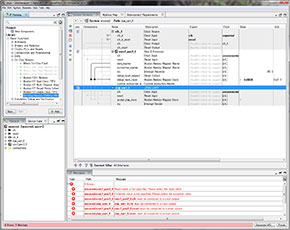

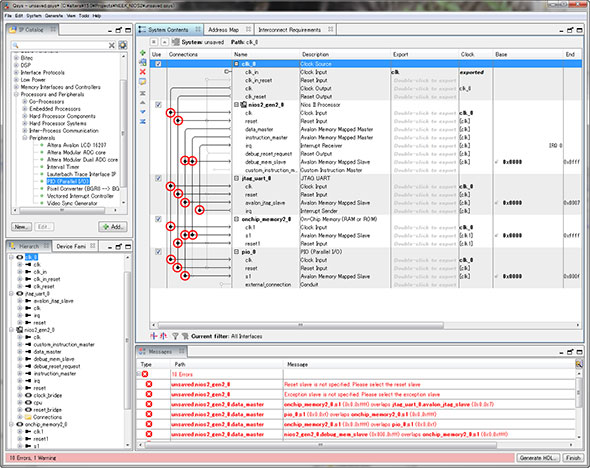

次に、それぞれのIPの結合を行う。Photo12で赤丸をつけてある箇所をクリックして、黒丸(結合状態)にする形だ。例えば一番左側の線はクロックドライバから出力されるクロック信号なので、これをNIOS II、JTAG_UART、On Chip Memory、PIOの各デバイスに供給するための設定がこれである。同様にReset出力、JTAGからNIOS IIへのIRQ、データの送受信など必要な配線をつなぐ形だ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す

FPGA開発において周辺機器(回路)は見落とせない要素の1つ。タッチパネルや各種出入力などを備えた「MAX 10 NEEK」を導入して、本格的な開発を目指す。 FPGAのソフトコアCPUをベンチマークで測定する

FPGAのソフトコアCPUをベンチマークで測定する

FPGA「MAX10」に「NIOS II」と呼ばれるソフトIPコアを導入することで、ソフトコアCPUを構築できる。ではその処理能力はどれほどか。ベンチマークソフトで測定してみよう。 FPGA上でソフトコアCPUを動かす手引き

FPGA上でソフトコアCPUを動かす手引き

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

単純なLチカならばFPGAでもそう難しくない。ただ、ダイナミック点灯やそれに伴うソースの最適化については“ならでは”のポイントが散見される。今回も連載で利用している「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAでのLチカをVerilog HDLで理解する

FPGAでのLチカをVerilog HDLで理解する

今回はFPGAでのLチカを例に、FPGA開発に必要なハードウェア記述言語の解説をしたい。用いる「Verilog HDL」はArduinoやCの経験がある方なら、理解そのものはそう難しくないと思う。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 「MAX 10 FPGA」のテスト環境を構築する

「MAX 10 FPGA」のテスト環境を構築する

今回から実際に「MAX 10 FPGA評価キット」を利用しての開発に着手する。まずは環境構築だ。キット以外に必要なモノもあるので注意して欲しい。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。