FPGAのソフトコアCPUをベンチマークで測定する:MAX 10 FPGAで学ぶFPGA開発入門(7)(4/6 ページ)

FPGA「MAX10」に「NIOS II」と呼ばれるソフトIPコアを導入することで、ソフトコアCPUを構築できる。ではその処理能力はどれほどか。ベンチマークソフトで測定してみよう。

ビルドしてDhrystoneを実行

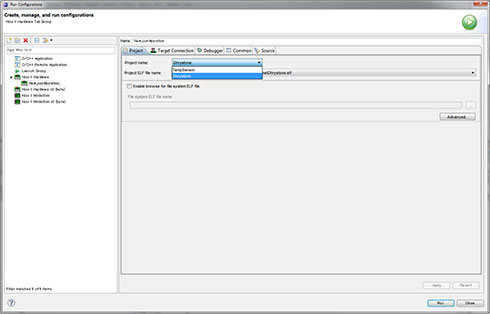

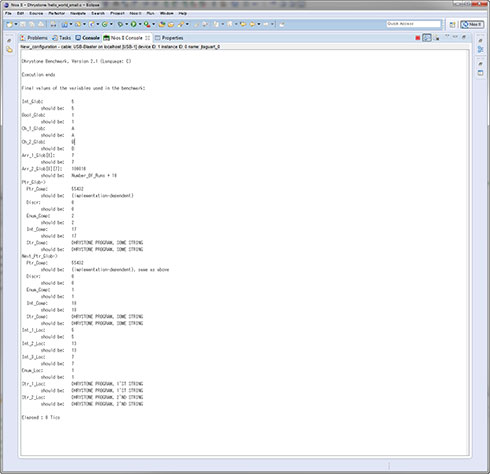

さて、これをビルドして実行であるが、Run Configurationの前に実行するプロジェクトをキチンと切り替えておくことを忘れずに(Photo05)。切り替えて実行したところ、見事にDhrystoneが完走した(Photo06)。

ただ、走った事はいいのだが、肝心の時間測定ができていない。実はalt_timestamp()はシステム・クロック(のTimestamp Timer)が利用できないと戻り値が0になる仕様なので、これの対応を追加してやる必要がある。

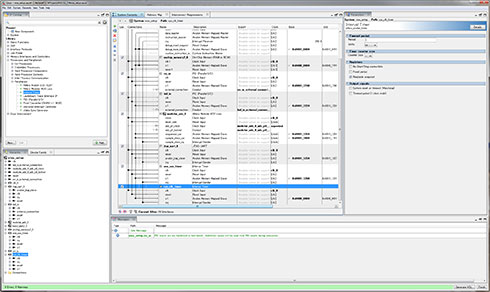

ということで、再びQSYSに戻る。QSYSは現状この状態になっていて、よく見ると「one_sec_timer」なるInterval Timerが既に存在しているのだが、こちらは1秒単位での測定しかしないものなので、もう少し細かい精度がほしい。

そこで左上からProcessors and Peripherals → Peripherals→ Interval Timer と選び、もう1つInterval Timerを追加した(Photo06)。こちらは右ペインにあるように、Periodを1μsとしたので、かなり細かく数字が取れるはずだ。

ちなみに配線としてclk/reset/s1/irqの各配線はone_sec_timerと同じようにつないでおく。以上が完了したら右下の「Generate HDL」ボタンを押して設定ファイルを生成、ついでQuartus IIの画面に戻ってビルドをやり直し、最後にProgrammerを使ってMAX 10に書き込むところまでを繰り返す。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

FPGA上でソフトコアCPUを動かす手引き

FPGA上でソフトコアCPUを動かす手引き

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

単純なLチカならばFPGAでもそう難しくない。ただ、ダイナミック点灯やそれに伴うソースの最適化については“ならでは”のポイントが散見される。今回も連載で利用している「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAでのLチカをVerilog HDLで理解する

FPGAでのLチカをVerilog HDLで理解する

今回はFPGAでのLチカを例に、FPGA開発に必要なハードウェア記述言語の解説をしたい。用いる「Verilog HDL」はArduinoやCの経験がある方なら、理解そのものはそう難しくないと思う。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 「MAX 10 FPGA」のテスト環境を構築する

「MAX 10 FPGA」のテスト環境を構築する

今回から実際に「MAX 10 FPGA評価キット」を利用しての開発に着手する。まずは環境構築だ。キット以外に必要なモノもあるので注意して欲しい。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。