連載

FPGA上でソフトコアCPUを動かす手引き:MAX 10 FPGAで学ぶFPGA開発入門(6)(3/7 ページ)

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。

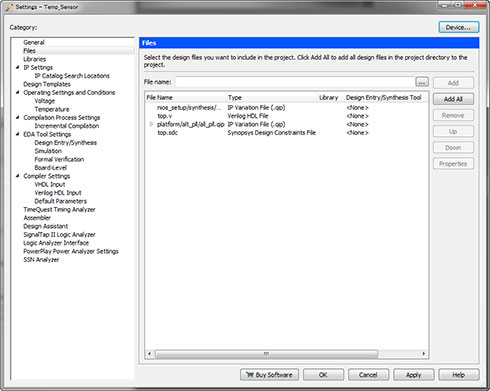

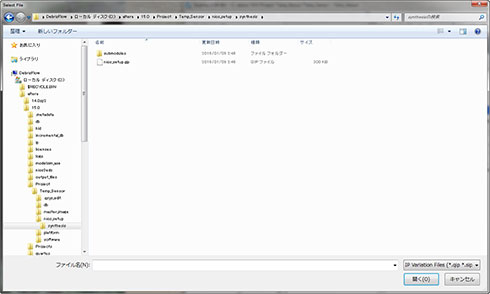

まずは生成されたnios_setup.qipをプロジェクトに追加してやる必要がある。これは「Project」→「Add/Remove Files in Project..."でnios_setup.qipを指定してやると(Photo15)、ファイル一覧に追加されたのが確認できる(Photo16)。

Photo15:ちなみに標準だと右下にあるファイル名のフィルターが"Design Files"(.tdf/.vhd/.v/...)になっているので、ここを"IP Variation Files"に切り替えないと見つからない

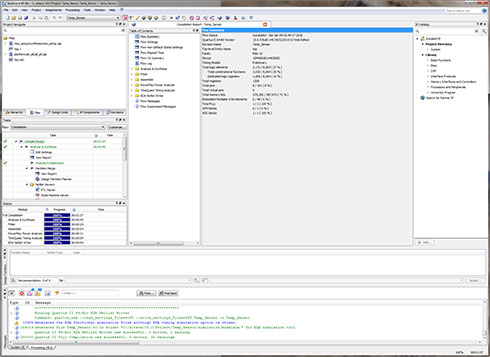

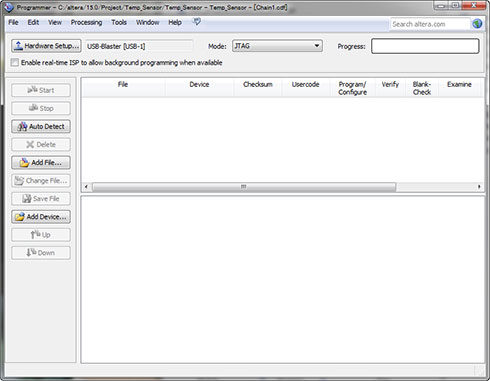

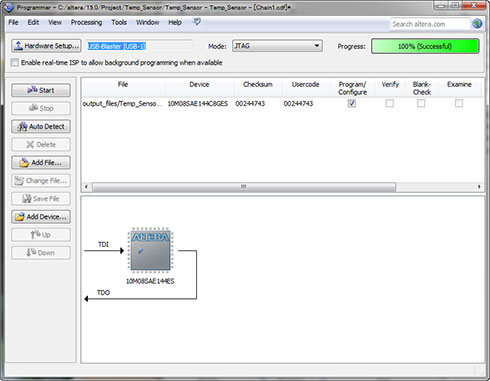

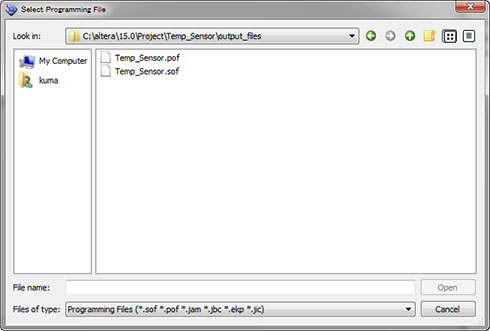

以上で、Quartus II側の作業は(おおむね)終了である。後は「Processing」→「Start Compilation」を選んで、FPGA側の全コンパイルをかける。問題がなければ正常にコンパイルが完了した旨が表示されるので(Photo17)、「Tool」→「Programmer」でProgrammerを起動し(Photo18)、「Add File...」で作成したsofファイルを指定して(Photo19)から「Start」ボタンを押す。手順を間違えてなければ、無事に完了するはずだ(Photo20)。

Photo19:生成したイメージはoutput_filesフォルダに生成されている。ちなみに.sofはRAMに書き込むイメージ、.pofはフラッシュメモリに書き込むイメージだが、今回はRAMに直接書き込みということで.sofの方を選択する

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 「MAX 10 FPGA」のテスト環境を構築する

「MAX 10 FPGA」のテスト環境を構築する

今回から実際に「MAX 10 FPGA評価キット」を利用しての開発に着手する。まずは環境構築だ。キット以外に必要なモノもあるので注意して欲しい。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。 いまさら聞けない FPGA入門

いまさら聞けない FPGA入門

あなたは、人に「FPGA」を正しく説明できるだろうか? いまや常識となりつつあるFPGAについて、あらためてその概念から仕組み、最新動向までを解説する。(編集部)