連載

FPGA上でソフトコアCPUを動かす手引き:MAX 10 FPGAで学ぶFPGA開発入門(6)(2/7 ページ)

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。

Nios IIの組み込み

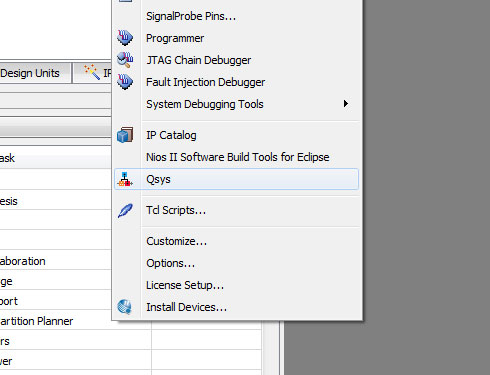

さて、それでは実際にNios IIの組み込みである。これを行うのはQsysというユーティリティーなので「Tools」メニューから起動する(Photo08)。

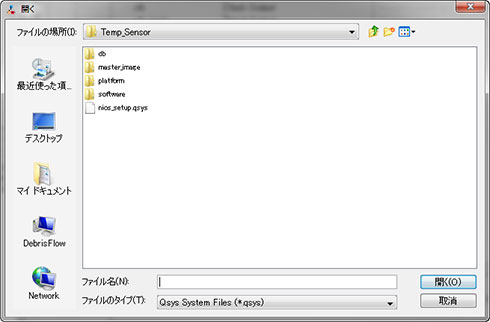

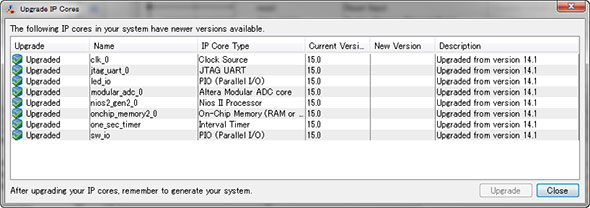

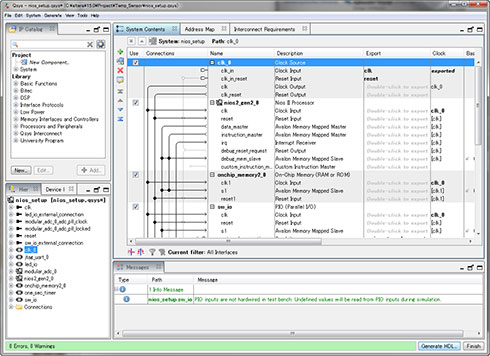

Qsysが起動すると、まずは設定ファイルの指定になる(Photo09)。ここで指定するものだが、先にTemplateからProjectを生成した際にnios_setup.qsysというファイルが生成されているのでこれを指定すると、しばらく処理を行った後、最終的にこんな情報を示して(Photo10)Qsysが立ち上がる(Photo11)。

この画面を注意深く見てもらうと分かるが、一番上がクロックモジュール、次がNios IIのコア、その下がオンチップのSRAM、という具合にモジュールが並び、さらにモジュール間でどの信号がどこに接続されるかがここで指定される。

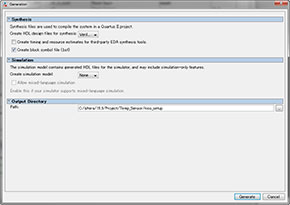

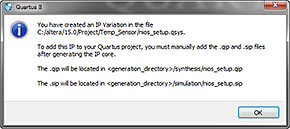

他にもアドレスマップや割り込みなども全部ここで設定されので、いろいろ設定を変えてみてもいいのだが、今のところは特に変更をせずに、右下の「Generate HD」ボタンを押すと、こんな確認が出る(Photo12)ので「Generate」を押す。しばらく処理が行われた後に、最終的にこんなダイアログが出てくる(Photo13)はずだ。これで、先に行方不明だったnios_setup.qipファイルが生成された事になる。

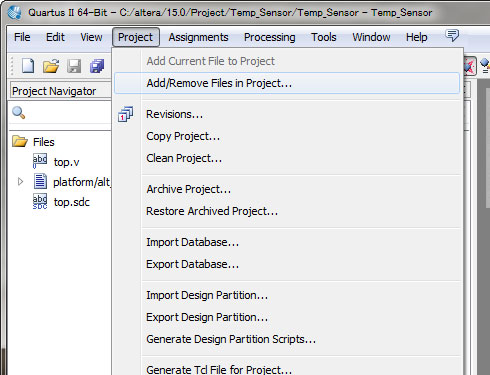

これでQsysの設定は完了。再びQuartus IIに戻る。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 「MAX 10 FPGA」のテスト環境を構築する

「MAX 10 FPGA」のテスト環境を構築する

今回から実際に「MAX 10 FPGA評価キット」を利用しての開発に着手する。まずは環境構築だ。キット以外に必要なモノもあるので注意して欲しい。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。 いまさら聞けない FPGA入門

いまさら聞けない FPGA入門

あなたは、人に「FPGA」を正しく説明できるだろうか? いまや常識となりつつあるFPGAについて、あらためてその概念から仕組み、最新動向までを解説する。(編集部)