組み込みコンピューティングに向けた、ハードウェアアクセラレーションの選択肢:SYSTEM DESIGN JOURNAL(4/6 ページ)

組み込みコンピューティングを加速させるハードウェア・アーキテクチャとは何でしょうか。DSP?GPU?それともメニーコアでしょうか。どのアプローチが最も適するのかを考察します。

我が道を行くGPU

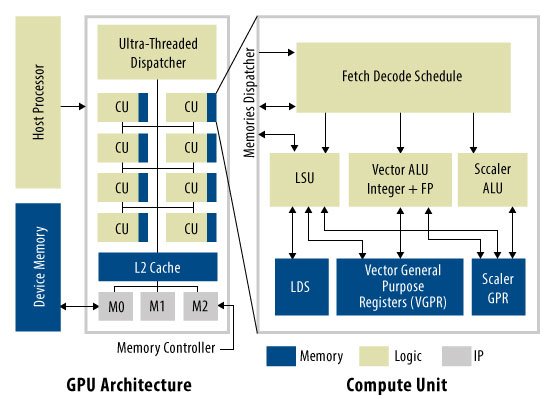

Hot ChipsではGPUアーキテクチャに関する論文も充実しており、AMDとARMは同じ考え方を共有していました。しかし、ここでの目的上、最も参考になった論文は、ウィスコンシン大学マディソン校のオープンソースGPUデザインに関するプレゼンテーションでしょう。レンダリングエンジンとしてよりもむしろ汎用GPUとして設計され、ネコの鳴き声のような名前が付けられた「MIAOW アーキテクチャ」は、頂点生成とテクスチャマッピングを専用ハードウェアに任せているため、基礎をなす並列コンピューティング・エンジンをより明確に示しています。

GPUアーキテクチャの複雑性を整理する方法の1つは、実は複雑化する一方のグラフィックスチップから出現したものではなく、Hexagonのような先進的DSPからの一連の進化段階と考えることです。

まず、多数の積和演算ユニットを並列実行し続けることができる非常に有機的な数値計算アプリケーションがあるとしましょう。多数のユニットということは、高解像度画像内の各ピクセルの色や強さを計算するようなアプリケーションです。この場合、Hexagonに非常によく似たエンジンで、より多くのALUを搭載し、固定小数点ではなく浮動小数点を得意とするエンジンが必要でしょう。DSPユニットの基本的なSIMDベクトル構成は問題なく、数を増やせばよいだけです。

広帯域ベクトルDSPは適するように思われますが、幾つかの課題があります。まず、1つの巨大SIMDエンジンの代わりに複数の大型SIMDエンジンを定義した方が、マシンの柔軟性が高まるはずです。超並列処理を利用できる場合は全て連携動作させ、中負荷のタスクが多数ある場合は独立動作させることが可能です。そのため、巨大同期ブロックのシリコン実装に伴う現実的問題もあって、GPU は通常、それぞれ独自のスレッドを持つことができる比較的独立した計算ユニット(Compute Units:CU)に分かれています。例えば、MIAOW (図 2)は8個のCUを備えています。小型のCUを多数搭載すると、1つの巨大SIMDマシンに比べて命令フェッチやデコードロジックに必要なリソースが増えますが、柔軟性が向上するため十分に見合います。

次の課題はゲート数です。こうしたベクトルパイプラインは全て多数のゲートを使用し、サポートするレジスタファイルも巨大になる他、消費電力も無視できません。SIMDアーキテクチャは、命令フェッチおよびデコードロジックの重複を最小限に抑えることで役立ちますが、MIAOWではフェッチデコード・スケジュールパイプラインが64個のベクトルALU、1個のスカラALU、1個のロード/ストア・ユニットの集合に対して1つしかありません。とはいえ、さらなる削減が必要です。

このCUと通常のCPUコアと比べた場合、明らかな違いが幾つかあります。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

FinFET革命がコンピュータアーキテクチャを変える

FinFET革命がコンピュータアーキテクチャを変える

FinFETの登場により、ムーアの法則はまだ継続される見通しです。ですが、それで全てが解決するわけではありません。FinFETの登場が、大きなSoCを自律的な機能ブロックに分割するという方向に導く結果となるでしょう。 サブシステムIPがチップの境界を越える

サブシステムIPがチップの境界を越える

サブシステム規模のIP(サブシステムIP)はSoCはもちろん、FPGAにまでも影響を与えています。素晴らしい取り組みですが、さまざまな注意点も存在します。スムーズな実装を行うための4つの注意点について述べます。 畳み込みニューラルネットワークの使い方、分かりますか?

畳み込みニューラルネットワークの使い方、分かりますか?

畳み込みニューラルネットワークとは何でしょうか。学問の世界から現実の世界に登場しつつあるこれは、さまざまな組み込みシステムに利用される可能性が高く、大いに関心を持つべきです。 組み込みにおけるコンピュータビジョンを整理する

組み込みにおけるコンピュータビジョンを整理する

画像認識(コンピュータビジョン、マシンビジョン)の需要は高まっており、その方法はさまざまです。画像による入力を有用なものとする実装方法について分類と整理を試みます。 モノのインターネットを再考する

モノのインターネットを再考する

IoTがその現実性について語られるようになった2015年、その基本概念を再考する機運が高まっています。「センサー」「仮想化」「フォグ」などの観点から、IoTを再考してみましょう。