組み込みコンピューティングに向けた、ハードウェアアクセラレーションの選択肢:SYSTEM DESIGN JOURNAL(3/6 ページ)

組み込みコンピューティングを加速させるハードウェア・アーキテクチャとは何でしょうか。DSP?GPU?それともメニーコアでしょうか。どのアプローチが最も適するのかを考察します。

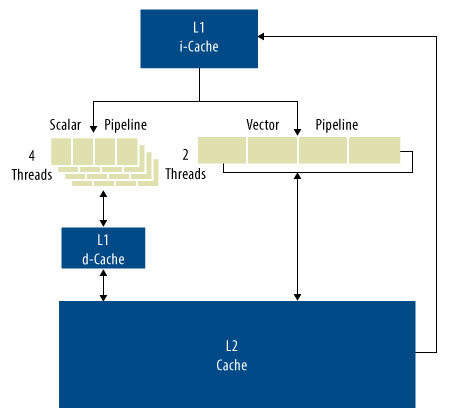

Qualcomm技術担当シニア・ディレクターのLucian Codrescu氏は、同社のSnapdragon SoCに使用されているHexagon HVX DSPコアの最新版について述べています(図 1)。要約を読むと、4スロットVLIW(Very Long Instruction Word)、スカラおよび1024bitベクトルSIMDパイプライン、4Wayマルチスレッディングなど、まるでアーキテクチャに関する最新アイデアの調査報告書のようです。

さらに、マイクロアーキテクトは、ビジョン処理アクセラレータとしてのHVXの役割に特有と思われる幾つかの選択を行っています。

1つは、スカラ/ベクトルパイプラインが浮動小数点ではなく整数であることです。「これらのアプリケーションの大部分では浮動小数点は必要ないため、ハードウェアに実装しないことで消費電力を抑えることを選びました」と Codrescu 氏は説明しています。

もう1つは少し珍しいキャッシュアーキテクチャです。スカラユニットは、メガバイトスケールのL2とコヒーレントな通常のL1命令/データキャッシュに接続されています。ベクトルユニットはL1命令キャッシュによってドライブされますが、L1データキャッシュはバイパスしてL2に直接接続されており、そこからデータの読み出し/書き込みを行います。これは、ベクトルSIMDユニットには主にピクセルデータのストリーミングを担当させることに加え、カスケードしてL1経由で一度に駆動するよりも、低速ながら大型のL2経由でピクセルをストリーミングする方がはるかに効率的という考え方のようです。

この推測を裏付けるように、L2はカメラセンサーからキャッシュ、キャッシュからチップ上の他の場所にある専用画像信号プロセッサにピクセルをトランスポートする「スマートデータムーバー」に接続されています。L2はARMシステムのメモリマネジャーにも接続されており、Hexagon L2、ARM CPU クラスタ、およびメインメモリ間での共有が可能です。

Codrescu 氏は、この仕組みとARMのNEON SIMDエンジンの類似性がかなり意図的なものであることを示唆しています。Qualcommは、C/C++コードとハンドクラフトアプリケーションライブラリを基本的なアプローチとして、POSIXのようなスレッド、さらにはLLVM(Low-Level Virtual Machine)コンパイルチェーンと、NEONプログラミングモデルの維持に向けてあらゆる努力をしています。興味深いことに、同社は並列画像処理用のドメイン特化型言語であるHalideの開発も行っています。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

FinFET革命がコンピュータアーキテクチャを変える

FinFET革命がコンピュータアーキテクチャを変える

FinFETの登場により、ムーアの法則はまだ継続される見通しです。ですが、それで全てが解決するわけではありません。FinFETの登場が、大きなSoCを自律的な機能ブロックに分割するという方向に導く結果となるでしょう。 サブシステムIPがチップの境界を越える

サブシステムIPがチップの境界を越える

サブシステム規模のIP(サブシステムIP)はSoCはもちろん、FPGAにまでも影響を与えています。素晴らしい取り組みですが、さまざまな注意点も存在します。スムーズな実装を行うための4つの注意点について述べます。 畳み込みニューラルネットワークの使い方、分かりますか?

畳み込みニューラルネットワークの使い方、分かりますか?

畳み込みニューラルネットワークとは何でしょうか。学問の世界から現実の世界に登場しつつあるこれは、さまざまな組み込みシステムに利用される可能性が高く、大いに関心を持つべきです。 組み込みにおけるコンピュータビジョンを整理する

組み込みにおけるコンピュータビジョンを整理する

画像認識(コンピュータビジョン、マシンビジョン)の需要は高まっており、その方法はさまざまです。画像による入力を有用なものとする実装方法について分類と整理を試みます。 モノのインターネットを再考する

モノのインターネットを再考する

IoTがその現実性について語られるようになった2015年、その基本概念を再考する機運が高まっています。「センサー」「仮想化」「フォグ」などの観点から、IoTを再考してみましょう。