第30回 インターポーザ:前田真一の最新実装技術あれこれ塾(4/4 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第30回は基板で処理しやすいパッド間隔やピン並びに変換する中継部品「インターポーザ」について解説する。

4.2.5D実装用インターポーザ基板

現在、インターポーザ基板としてビルドアップ基板が多く使われていますが、今後の2.5D実装や3D実装ではシリコンインターポーザという声が大きく、ビルドアップ基板を使った実装は聞こえてきません。

現在、チップのパッドは100〜120μm程度になっています。最先端では100μm以下のピッチがありますが、これが2.5D、3D実装が普通に使われるようになると、50μmから、最先端では25μmまでを視野に入れた開発が必要だといわれています。

このようなファインピッチに対応するためには配線幅が10μm以下、ビアが25μm程度が実現できる基板技術が必要とされます。

このように細い配線を精度良く整形するためには基板表面の平滑度が問題となります。

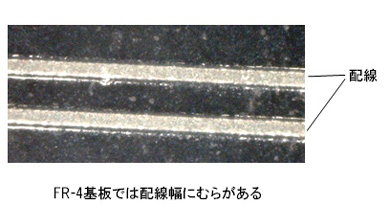

表面に凹凸があると、配線の幅は凹凸に合わせてムラが生じます(図16)。

これは、パターン成形のマスクが密着しなかったり、エッチングが厚さムラに応じてムラになったりと多くの原因があります。

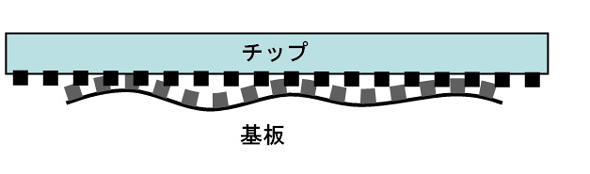

また、表面が平滑でないと小さなチップパッドとの接続も信頼性が低下します(図17)。

次に、熱膨張率の問題があります。

10μm以下の配線幅の導体や小さなチップパッドでの接続は脆弱で、基板が熱膨張によって、大きく寸法が変化するようでは信頼性が低下します。

同様に、熱対策ですが、基板材料としては熱伝導率ができるだけ高い必要があります。

チップが発生した熱を効率よく放熱する必要があります。

もちろん、材料コストや、製造容易性、電気特性(低誘電率、低損失、インピーダンスマッチング、低抵抗)などの特性も必要です。

特に、配線幅が非常に細い場合、配線の特性インピダンスの制御と、直流抵抗による損失には注意が必要です。

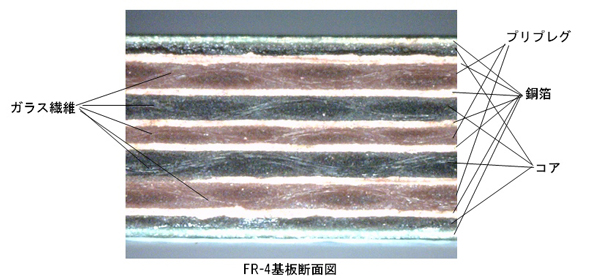

残念ながら、ガラスエポキシを使ったビルドアップ基板ではガラス繊維の織りのため、高度の平滑度は得られません(図18)。

ガラス繊維は基板の強度を保ち、温度変化による熱膨張や変形を抑えるため欠かせない芯材です。

このため、現在、2.5D実装や3D実装用のインターポーザ基板としてシリコン基板が良く使われています。また、それほどパッドピッチがファインでないMCM(Multi Chip Module)ではビルドアップ基板が使われています。

シリコン基板では特にTSV(Through Silicon Via)と呼び、ビアの製造が問題になっていますが、インターポーザ基板ではビアは必須の要素で、ビアの穴あけや導通の製造コストと信頼性は重要な項目となります。

また、チップの大型化によって、インターポーザ基板も大きくなります。特にチップを平面状に配置する2.5D実装ではインターポーザ基板は結構大きくなります。

今後のインターポーザ基板の材料としてはシリコンだけではなくいくつかの材料が候補としてあがっています。 表面平滑性の得られる材料として、ガラスコアを使わなくても良いポリイミドなどの有機材料、ガラス、セラミック、金属、多結晶(SC=Single Crystal)シリコン、多結晶(ポリ)シリコンなどです。

これらの材料にはおのおの短所、長所があり今後、どれがインターポーザ基板に使われるのか、目的と特徴に応じて使い分けが進むのかは不明です。

参考文献2にこれらの材料の比較が載っているので、それを基に少し変えた比較を表1に示します。

現在、例えば液晶基板には一般的にガラス基板が使われています。今後、これらのインターポーザ用基板に開発されている基板が現在のPCBに使われてる分野にも広がってゆく可能性もあります。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- ≫前田真一の最新実装技術あれこれ塾

第25回 量産技術化が進むTSV

第25回 量産技術化が進むTSV

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第25回は、量産技術として開発が加速しているTSV(Through Silicon Via)の最新動向を解説する。 MPUとの連携で存在感を強めるザイリンクスのFPGA

MPUとの連携で存在感を強めるザイリンクスのFPGA

東京エレクトロン デバイスは2011年2月16日、東京都内でプライベートカンファレンス「TEDプログラマブル・ソリューション 2011」を開催。パートナ企業とともに、FPGAに関する最新の技術・ソリューションを披露した。特に目を引いた「MPUとFPGAの連携」の部分をレポートする。(編集部)